- 您現在的位置:買賣IC網 > PDF目錄98216 > THS10064CDA (TEXAS INSTRUMENTS INC) 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 PDF資料下載

參數資料

| 型號: | THS10064CDA |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| 封裝: | GREEN, PLASTIC, TSSOP-32 |

| 文件頁數: | 21/42頁 |

| 文件大?。?/td> | 527K |

| 代理商: | THS10064CDA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

THS10064

SLAS255B – DECEMBER 1999 – REVISED DECEMBER 2002

www.ti.com

28

DATA_AV TYPE

Bit 4 and bit 5 (DATA_T, DATA_P) of control register 1 are used to program the signal DATA_AV. Bit 4 of

control register 1 determines whether the DATA_AV signal is static or a pulse. Bit 5 of the control register determines

the polarity of DATA_AV. This is shown in Table 14.

Table 14. DATA_AV Type

BIT 5

DATA_P

BIT 4

DATA_T

DATA_AV TYPE

0

Active low level

0

1

Active low pulse

1

0

Active high level

1

Active high pulse

The signal DATA_AV is set to active when the trigger condition is satisfied. It is set back inactive dependent of the

DATA_T selection (pulse or level).

If level mode is chosen, DATA_AV is set inactive after the first of the TL (TL = trigger level) reads (with the falling edge

of READ). The trigger condition is checked again after TL reads. For single conversion mode, DATA_AV type should

be programmed to active level mode.

If pulse mode is chosen, the signal DATA_AV is a pulse with a width of one half of a CONV_CLK cycle in continuous

conversion mode. The next DATA_AV pulse (when the trigger condition is satisfied) is sent out the earliest, when the

TL values, written into the FIFO before, were read out by the processor.

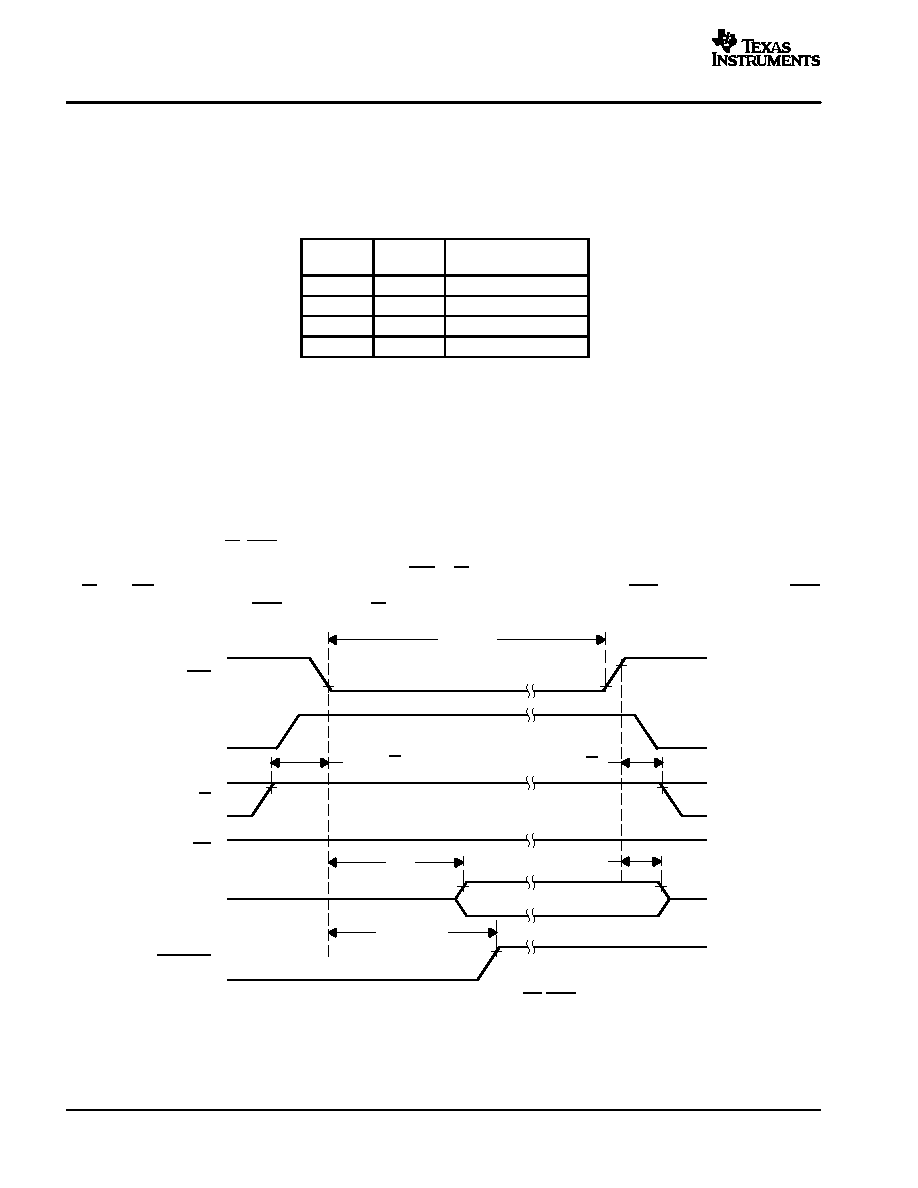

Read Timing (using R/W, CS0-controlled)

Figure 38 shows the read-timing behavior when the WR(R/W) input is programmed as a combined read-write input

R/W. The RD input has to be tied to high-level in this configuration. This timing is called CS0-controlled because CS0

is the last external signal of CS0, CS1, and R/W which becomes valid.

90%

10%

tw(CS)

tsu(R/W)

th(R/W)

ta

th

td(CSDAV)

CS0

CS1

R/W

RD

D(0–9)

DATA_AV

Figure 38. Read Timing Diagram Using R/W (CS0-controlled)

相關PDF資料 |

PDF描述 |

|---|---|

| THS10064IDA | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS10064CDAR | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS10064IDAR | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS10064IDAG4 | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1007CDA | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| THS10064CDAG4 | 功能描述:模數轉換器 - ADC 10-Bit 6 MSPS Quad Ch DSP/uP Ifc RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS10064CDAR | 功能描述:模數轉換器 - ADC 10-Bit 6 MSPS Quad Ch DSP/uP Ifc RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS10064CDARG4 | 功能描述:模數轉換器 - ADC 10-Bit 6 MSPS Quad Ch DSP/uP Ifc RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS10064DA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT 6 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS10064EVM | 制造商:Texas Instruments 功能描述:THS10064 10-BIT, 6 MSPS, DC EVM - Bulk |

發布緊急采購,3分鐘左右您將得到回復。