- 您現在的位置:買賣IC網 > PDF目錄98252 > TLV320AIC10CPFB (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP48 PDF資料下載

參數資料

| 型號: | TLV320AIC10CPFB |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| 封裝: | GREEN, PLASTIC, TQFP-48 |

| 文件頁數: | 17/57頁 |

| 文件大小: | 454K |

| 代理商: | TLV320AIC10CPFB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

2–10

2.7.4

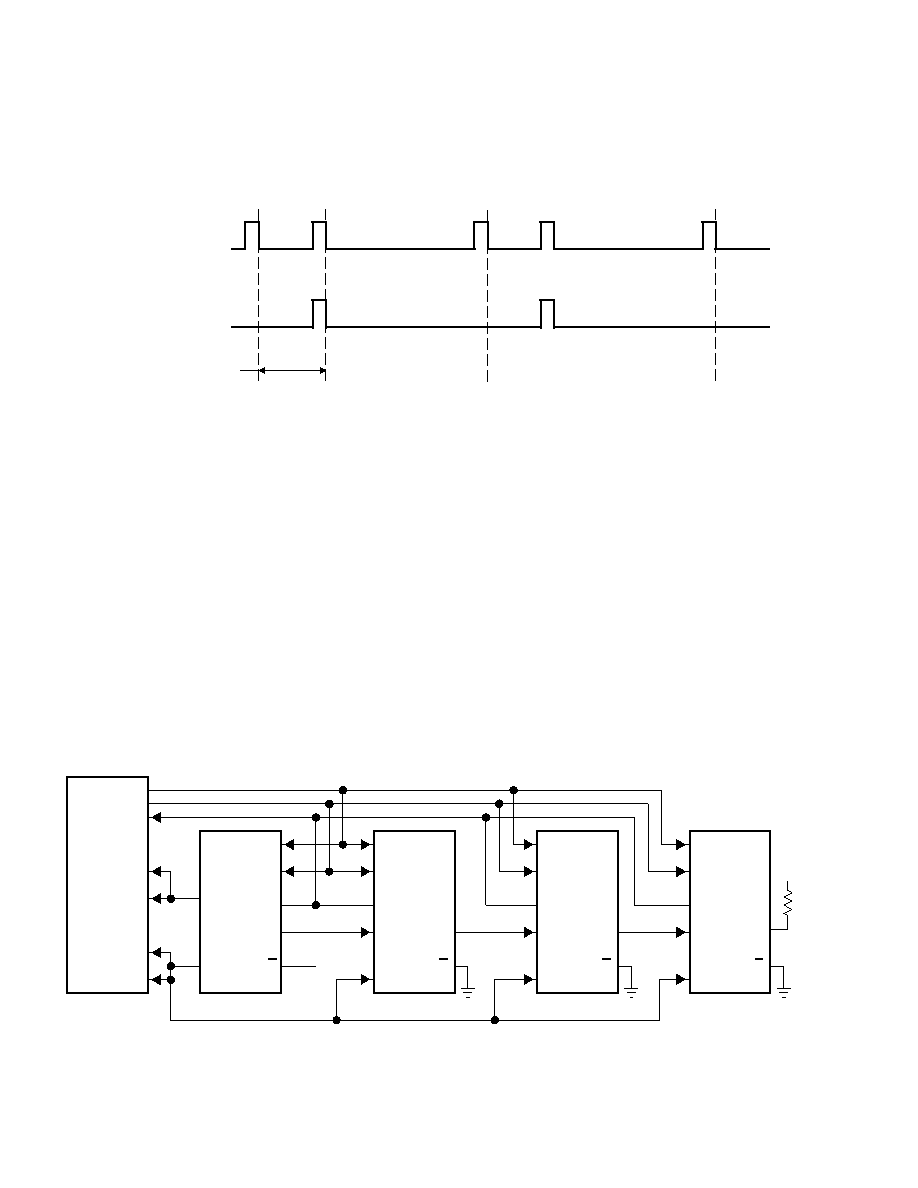

Frame-Sync (FS) Function—Slave Mode

The slave mode is selected by connecting pin M/S to LO. The frame-sync timing is generated externally by the master,

as shown in Figure 2–13 (that is, FSD) and is applied to FS of the slave to control the ADC and DAC timing.

MP

32 SCLKs

FSD (Master)

to FS (Slave)

FS

(Master to DSP)

SP

MS

SS

MP

NOTE: MP: master primary (master-device data is transferred during this period, the DOUT of the slave device is in high-impedance state).

SP: slave primary (slave device data is transferred during this period, the DOUT of master device is in high-impedance state).

MS: master secondary (master device control register information is transferred during this period, the DOUT of slave device is in high-

impedance state).

SS: slave secondary (slave device control register information is transferred during this period, the DOUT of master device is in high-

impedance state).

Figure 2–13. Master Device’s FS Output to DSP and FSD Output to the Slave

2.7.5

Frame-Sync Delayed (FSD) Function, Cascade Mode

In cascade mode, the DSP must be able to identify the master and slaves according to the register map shown in

Appendix A. Each device in the cascade contains a 3-bit cascade register (D15-D13 in the register address) that has

been programmed by the ACD (automatic cascade detection) with an address value equal to its position in the

cascade during the device’s power-up initialization (see Appendix A). The device address of the master is always

equal to the number of slaves in the cascade. For example, in Figure 2–14, D15-D13 of the master is 011, as shown

in row 4 of Table A-1 (Appendix A). The DSP receives all frame-sync pulses from the master though the masters FS.

The master FSD is output to the first slave, and the first slave FSD is output to the second slave device, and so on.

Figure 2–14 shows the cascade of 4 TLV320AIC10s in which the closest one to the DSP is the master, and the rest

are slaves. The FSD output of each device is input to the FS terminal of the succeeding device. Figure 2–15 shows

the FSD timing sequence in the cascade.

MCLK

DIN

DOUT

FS

SCLK

MCLK

DIN

DOUT

FS

SCLK

MCLK

DIN

DOUT

FS

SCLK

Slave 2

Slave 1

Slave 0

Master

MCLK

DIN

DOUT

FSD

SCLK

FSD

FS

CLKOUT

DX

DR

FSX

FSR

CLKX

CLKR

TMS320C54XX

DVDD

FSD

M/S

(or Master Clock Source)

DVDD

1 k

Figure 2–14. Cascade Mode Connection (to DSP Interface)

相關PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC10IPFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV320AIC10CGQE | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC10IGQE | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC10CGQER | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC10IGQER | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV320AIC10CPFBG4 | 功能描述:接口—CODEC 16-Bit Reg Trnscvr With 3-State Outputs RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC10EVM | 功能描述:音頻 IC 開發工具 TLV320AIC10 Eval Mod RoHS:否 制造商:Texas Instruments 產品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

| TLV320AIC10I | 制造商:TI 制造商全稱:Texas Instruments 功能描述:General-Purpose 3V to 5.5V 16-bit 22-KSPS DSP CODEC |

| TLV320AIC10IGQER | 功能描述:接口—CODEC 16-Bit 22-KSPS DSP Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC10IPFB | 功能描述:接口—CODEC 16-Bit 22-KSPS DSP Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。