- 您現在的位置:買賣IC網 > PDF目錄382646 > TMJ320C6211GDP167 (Texas Instruments, Inc.) FIXED-POINT DIGITAL SIGNAL PROCESSORS PDF資料下載

參數資料

| 型號: | TMJ320C6211GDP167 |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數字信號處理 |

| 英文描述: | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| 中文描述: | 定點數字信號處理器 |

| 文件頁數: | 60/83頁 |

| 文件大小: | 1176K |

| 代理商: | TMJ320C6211GDP167 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁

TMS320C6211, TMS320C6211B

FIXED-POINT DIGITAL SIGNAL PROCESSORS

SPRS073K

AUGUST 1998

REVISED MARCH 2004

60

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251

1443

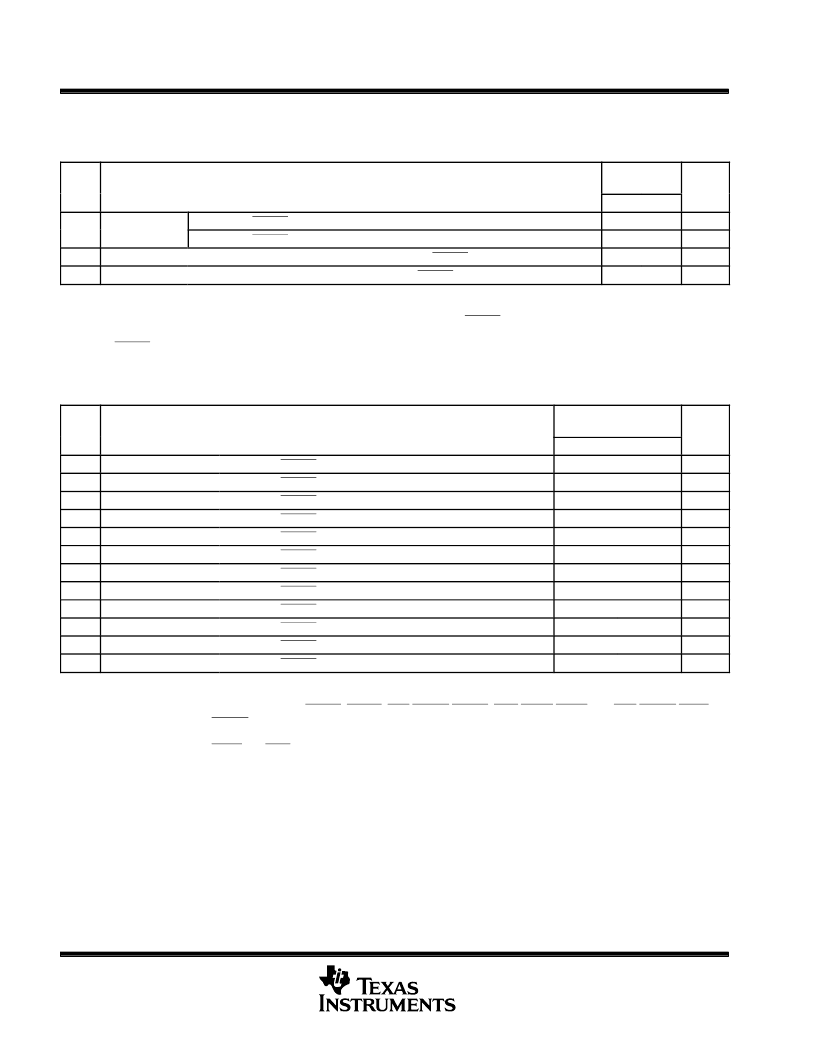

RESET TIMING

timing requirements for reset

(see Figure 31)

NO.

150

167

UNIT

MIN

10P

250

2P

2P

MAX

1

t

w(RST)

Width of the RESET pulse (PLL stable)

Width of the RESET pulse (PLL needs to sync up)

§

Setup time, HD boot configuration bits valid before RESET high

Hold time, HD boot configuration bits valid after RESET high

P = 1/CPU clock frequency in ns. For example, when running parts at 167 MHz, use P = 6 ns.

This parameter applies to CLKMODE x1 when CLKIN is stable, and applies to CLKMODE x4 when CLKIN and PLL are stable.

§

This parameter applies to CLKMODE x4 only (it does not apply to CLKMODE x1). The RESET signal is not connected internally to the clock PLL

circuit. The PLL, however, may need up to 250

μ

s to stabilize following device power up or after PLL configuration has been changed. During

that time, RESET must be asserted to ensure proper device operation. See the

clock PLL

section for PLL lock times.

HD[4:3] are the boot configuration pins during device reset.

ns

μ

s

ns

ns

14

15

t

su(HD)

t

h(HD)

switching characteristics over recommended operating conditions during reset

#||

(see Figure 31)

NO.

PARAMETER

150

167

UNIT

MIN

MAX

2

3

4

5

6

7

8

9

10

11

12

13

t

d(RSTL-ECKI)

t

d(RSTH-ECKI)

t

d(RSTL-EMIFZHZ)

t

d(RSTH-EMIFZV)

t

d(RSTL-EMIFHIV)

t

d(RSTH-EMIFHV)

t

d(RSTL-EMIFLIV)

t

d(RSTH-EMIFLV)

t

d(RSTL-HIGHIV)

t

d(RSTH-HIGHV)

t

d(RSTL-ZHZ)

t

d(RSTH-ZV)

Delay time, RESET low to ECLKIN synchronized internally

Delay time, RESET high to ECLKIN synchronized internally

Delay time, RESET low to EMIF Z group high impedance

Delay time, RESET high to EMIF Z group valid

Delay time, RESET low to EMIF high group invalid

Delay time, RESET high to EMIF high group valid

Delay time, RESET low to EMIF low group invalid

Delay time, RESET high to EMIF low group valid

Delay time, RESET low to high group invalid

Delay time, RESET high to high group valid

Delay time, RESET low to Z group high impedance

Delay time, RESET high to Z group valid

2P + 3E

2P + 3E

2P + 3E

3P + 4E

3P + 4E

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

3P + 4E

2P + 3E

3P + 4E

2P + 3E

3P + 4E

2P

4P

2P

2P

P = 1/CPU clock frequency in ns. For example, when running parts at 167 MHz, use P = 6 ns.

#

E = ECLKIN period in ns

||

EMIF Z group consists of:

EA[21:2], ED[31:0], CE[3:0], BE[3:0], ARE/SDCAS/SSADS, AWE/SDWE/SSWE, and AOE/SDRAS/SSOE

EMIF high group consists of: HOLDA

EMIF low group consists of:

BUSREQ

High group consists of:

HRDY and HINT

Z group consists of:

HD[15:0], CLKX0, CLKX1, FSX0, FSX1, DX0, DX1, CLKR0, CLKR1, FSR0, FSR1, TOUT0, and TOUT1.

相關PDF資料 |

PDF描述 |

|---|---|

| TMJ320C6211GFN167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMJ320C6211GHK167 | CONNECTOR ACCESSORY |

| TMJ320C6211GJL167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMJ320C6211GLS167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMJ320C6211GLW167 | CONNECTOR ACCESSORY |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TMJ320C6211GFN167 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMJ320C6211GGP167 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMJ320C6211GHK167 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMJ320C6211GJC167 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMJ320C6211GJL167 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

發布緊急采購,3分鐘左右您將得到回復。