- 您現在的位置:買賣IC網 > PDF目錄98287 > TS(X)8387CF 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 PDF資料下載

參數資料

| 型號: | TS(X)8387CF |

| 元件分類: | ADC |

| 英文描述: | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 封裝: | CERAMIC, QFP-68 |

| 文件頁數: | 21/38頁 |

| 文件大小: | 617K |

| 代理商: | TS(X)8387CF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

TS8387

28/38

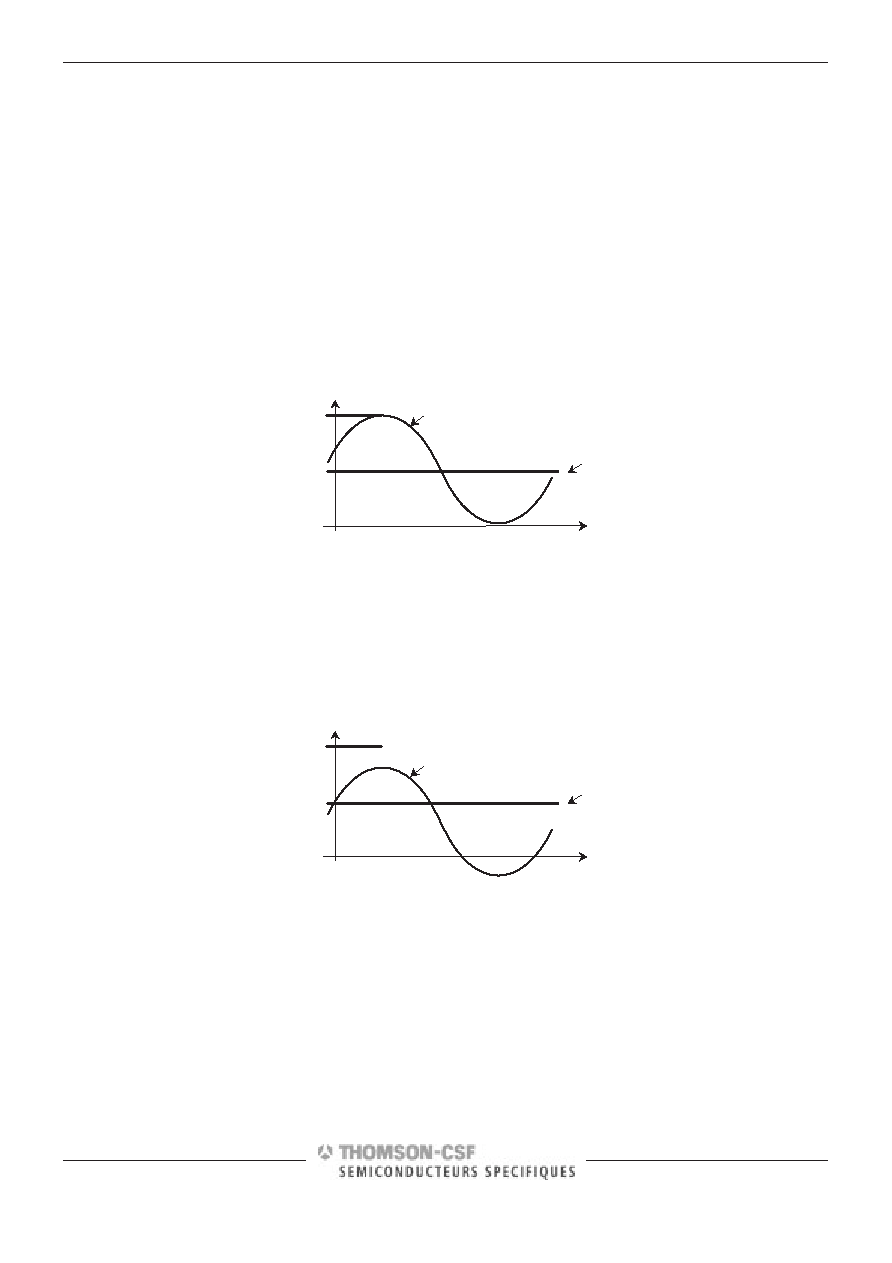

7.3.3.SINGLE ENDED CLOCK INPUT (Ground Common Mode)

An even more convenient clock input configuration is proposed below :

The TS8387 clock buffer can also manage a single-ended sinewave clock signal centered around 0 Volt.

(out of phase clock signal grounded through the 50 Ohm termination resistor).

The typical inphase clock input amplitude is 1 Volt peak to peak, centered on 0 Volt (ground) common mode.

This corresponds to a typical clock input power level of 4 dBm into the 50 ohms termination resistor.

Do not exceed 10 dBm to avoid saturation of the preamplifier input transistors.

The inverted phase clock input is grounded through the 50 ohms termination resistor.

Single ended Clock input (Ground common mode)

VCLK common mode = 0 Volt

VCLKB=0 Volt

4 dBm typical clock input power level

(into 50 ohms termination resistor)

[V]

t

VCLK

VCLKB = ( 0 V )

–0.5V

+0.5V

Note 1 : Do not exceed 10 dBm into the 50 ohms termination resistor for single clock input power level.

7.4.

CLOCK SIGNAL DUTY CYCLE ADJUST

In single ended configuration, when using a sinewave clock generator,the clock signal duty cycle can be easily adjusted

by simply offseting the inphase clock signal using a biasing tee, (as the out of phase clock input is at ground level ).

Single ended Clock input (Inphase clock input common mode shifted)

VCLK common mode = –180mV

VCLKB = 0 Volt

[V]

t

VCLK – 180 mV

VCLKB = ( 0 V )

–0.5V

40 %

60 %

+0.5V

Note 1 : Do not exceed 10 dBm into the 50 ohms termination resistor for single clock input power level.

Note 2 :For an input CLK signal of 4 dBm into 50 ohms, the typical offset value to achieve a 40 / 60 clock duty cycle is –180 mV on

CLK.

7.5.

NOISE IMMUNITY INFORMATIONS

Circuit noise immunity performance begins at design level.

Efforts have been made on the design in order to make the device as insensitive as possible to chip environment per-

turbations resulting from the circuit itself or induced by external circuitry.

(Cascode stages isolation, internal damping resistors, clamps, internal (onchip) decoupling capacitors.)

Furthermore, the fully differential operation from analog input up to the digital outputs provides enhanced noise immu-

nity by common mode noise rejection.

Common mode noise voltage induced on the differential analog and clock inputs will be canceled out by these balanced

differential amplifiers.

相關PDF資料 |

PDF描述 |

|---|---|

| TS8387MF | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS8387CF | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS(X)8387CF | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS8387CF_ | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS(X)8387CF_ | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TSX-8A16MHZ | 制造商:Epson Electronics America Inc 功能描述:CODE BCAI |

| TSX920ILT | 功能描述:General Purpose Amplifier 1 Circuit Rail-to-Rail SOT-23-6 制造商:stmicroelectronics 系列:- 包裝:剪切帶(CT) 零件狀態:有效 放大器類型:通用 電路數:1 輸出類型:滿擺幅 壓擺率:17 V/μs 增益帶寬積:10MHz -3db 帶寬:- 電流 - 輸入偏置:10pA 電壓 - 輸入失調:4mV 電流 - 電源:2.9mA 電流 - 輸出/通道:74mA 電壓 - 電源,單/雙(±):4 V ~ 16 V 工作溫度:-40°C ~ 125°C 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商器件封裝:SOT-23-6 標準包裝:1 |

| TSX921ILT | 制造商:STMicroelectronics 功能描述:ANALOG AND AUDIO SYSTEMS - Tape and Reel 制造商:STMicroelectronics 功能描述:ANALOG and AUDIO SYSTEMS |

| TSX921IYLT | 制造商:STMicroelectronics 功能描述:IC OPAMP R-R 10MHZ SOT23-5 |

| TSX922IDT | 功能描述:General Purpose Amplifier 2 Circuit Rail-to-Rail 8-SO 制造商:stmicroelectronics 系列:- 包裝:剪切帶(CT) 零件狀態:有效 放大器類型:通用 電路數:2 輸出類型:滿擺幅 壓擺率:17 V/μs 增益帶寬積:10MHz -3db 帶寬:- 電流 - 輸入偏置:10pA 電壓 - 輸入失調:4mV 電流 - 電源:2.8mA 電流 - 輸出/通道:74mA 電壓 - 電源,單/雙(±):4 V ~ 16 V 工作溫度:-40°C ~ 125°C 安裝類型:表面貼裝 封裝/外殼:8-SOIC(0.154",3.90mm 寬) 供應商器件封裝:8-SO 標準包裝:1 |

發布緊急采購,3分鐘左右您將得到回復。