- 您現在的位置:買賣IC網 > PDF目錄98301 > TS86101G2BMGS (E2V TECHNOLOGIES PLC) PARALLEL, WORD INPUT LOADING, 10-BIT DAC, CBGA255 PDF資料下載

參數資料

| 型號: | TS86101G2BMGS |

| 廠商: | E2V TECHNOLOGIES PLC |

| 元件分類: | DAC |

| 英文描述: | PARALLEL, WORD INPUT LOADING, 10-BIT DAC, CBGA255 |

| 封裝: | CI-CGA, 255 PIN |

| 文件頁數: | 56/57頁 |

| 文件大小: | 1030K |

| 代理商: | TS86101G2BMGS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁當前第56頁第57頁

8

0992D–BDC–04/09

TS86101G2B

e2v semiconductors SAS 2009

2.2

Timing Characteristics

Notes:

1. Digital input data rise/fall time: defined between 20% to 80%.

2. Exclusive of period (pp) jitter on both Data and on Data Ready.

3. CW_IN clock input jitter over 5 GHz bandwidth. MUXDAC also operates with CW_IN clock showing more jitter but this may

degrade performance (SNR and NPR).

4. Guaranteed by design.

6. TPD can be directly measured at package input/output, between CW_IN clock and analog output.

7. Full-scale analog output (10% to 90%).

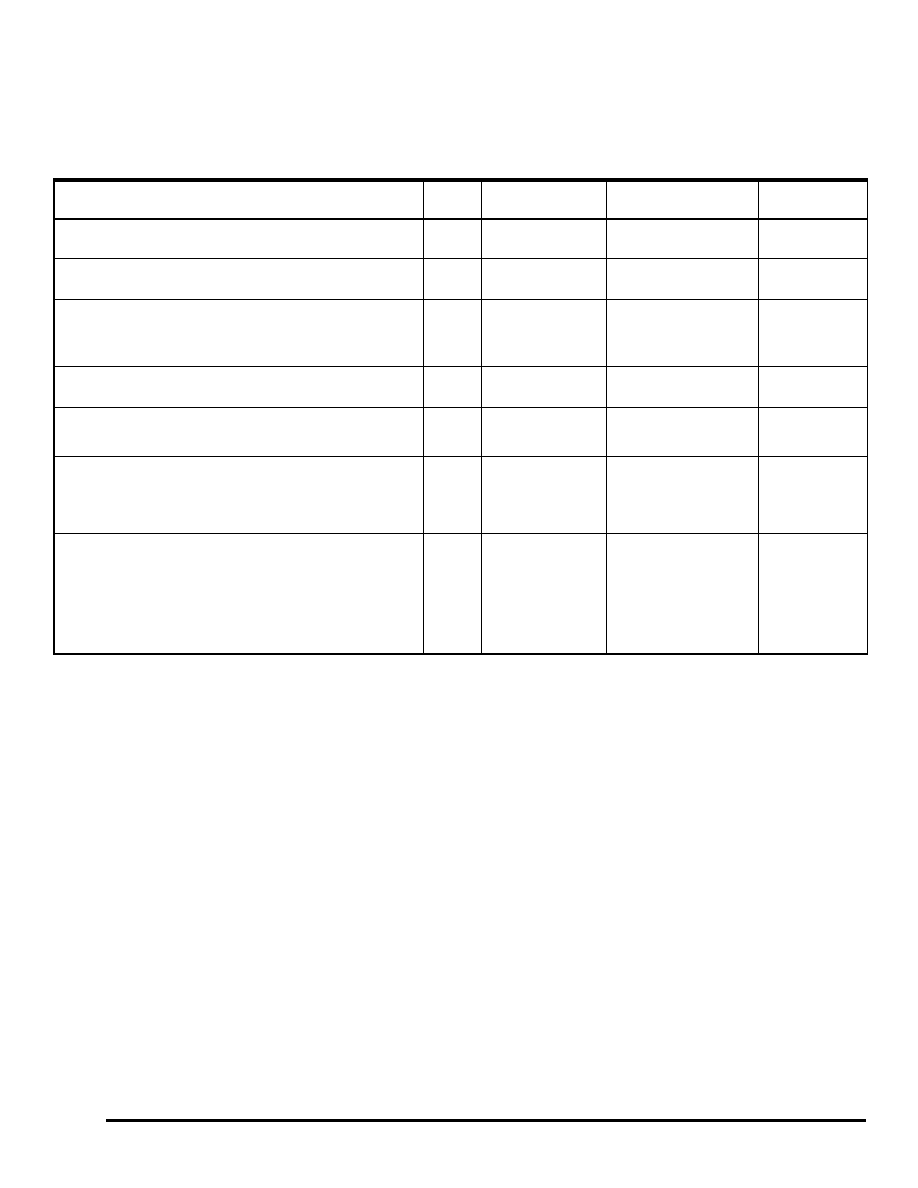

Table 2-4.

Timing Characteristics: 50

Ω // 2pF Loading Conditions on Each Single-ended Output. Absolute Timing

Values are Given at Package Input/Output Balls

Parameter

Test

Level

Min

Typ

Max

Data and data ready maximum allowable input jitter

4

300 ps peak- to-

peak

Input data rise/fall time(1)

Data ready rise/fall time(1)

4

500 ps

Tsetup(2) see Figure 5-2 on page 21

Thold(2) see Figure 5-2 on page 21

4

–1.3 ns

2.5 ns

Input data rate (ports A, B, C and D)

4

350 MWords/s

Input data pulse width (ports A, B, C and D)

4

5.7 ns

(at 350 MWord/s)

CW_IN clock input frequency

4

1400 MHz

CW_IN master clock input jitter

41 ps rms

CW_IN to DSP clock output delay with clock shift 0000

CW_IN to DSP clock output delay with clock shift 1111

DSP clock output phase tuning range

DSP clock output phase tuning steps

4

1

2.1 ns + 1 clock cycle

5.2 ns + 1 clock cycle

0 to 3.1 ns

200 ps

Data ready to CW_IN clock timing: (Figure 5-4 on page 22)

Forbidden area

4

600 ps

Pipeline delay(4)

TOD(5)

TPD(5)(6) (propagation delay)

Analog output rise/fall time(7)

4

1 clock cycle

3.7 ns

Pipeline delay + TOD

180 ps

相關PDF資料 |

PDF描述 |

|---|---|

| TS86101G2BVGL | PARALLEL, WORD INPUT LOADING, 10-BIT DAC, CBGA255 |

| TS86101G2BCGL | PARALLEL, WORD INPUT LOADING, 10-BIT DAC, CBGA255 |

| TSA0801IF | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| TSA0801CFT | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| TSA0801CF | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TS86101G2BVGL | 制造商:e2v technologies 功能描述:10-BIT DAC MUXDAC 10-BIT 1.2 GSPS - Trays |

| TS861AI | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:RAIL TO RAIL MICROPOWER BICMOS COMPARATORS |

| TS861AID | 功能描述:校驗器 IC Single Rail-to-Rail RoHS:否 制造商:STMicroelectronics 產品: 比較器類型: 通道數量: 輸出類型:Push-Pull 電源電壓-最大:5.5 V 電源電壓-最小:1.1 V 補償電壓(最大值):6 mV 電源電流(最大值):1350 nA 響應時間: 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SC-70-5 封裝:Reel |

| TS861AIDT | 功能描述:校驗器 IC Single Rail-to-Rail RoHS:否 制造商:STMicroelectronics 產品: 比較器類型: 通道數量: 輸出類型:Push-Pull 電源電壓-最大:5.5 V 電源電壓-最小:1.1 V 補償電壓(最大值):6 mV 電源電流(最大值):1350 nA 響應時間: 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SC-70-5 封裝:Reel |

| TS861AILT | 功能描述:校驗器 IC Single Rail-to-Rail RoHS:否 制造商:STMicroelectronics 產品: 比較器類型: 通道數量: 輸出類型:Push-Pull 電源電壓-最大:5.5 V 電源電壓-最小:1.1 V 補償電壓(最大值):6 mV 電源電流(最大值):1350 nA 響應時間: 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SC-70-5 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。