- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68800 > 5962-9864601QEX (ANALOG DEVICES INC) LOG OR ANTILOG AMPLIFIER, 395 MHz BAND WIDTH, CDIP16 PDF資料下載

參數(shù)資料

| 型號: | 5962-9864601QEX |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 模擬運算功能 |

| 英文描述: | LOG OR ANTILOG AMPLIFIER, 395 MHz BAND WIDTH, CDIP16 |

| 封裝: | SIDE BRAZED, CERAMIC, DIP-16 |

| 文件頁數(shù): | 2/16頁 |

| 文件大小: | 397K |

| 代理商: | 5962-9864601QEX |

REV. A

AD8306

–10–

low frequency applications, a simple RC network forming a low-

pass filter should be added at the input for the same reason.

If the limiter output is not required, Pin 9 (LMDR) should be

left open and Pins 12 and 13 (LMHI, LMLO) should be tied to

VPS2 as shown in Figure 24.

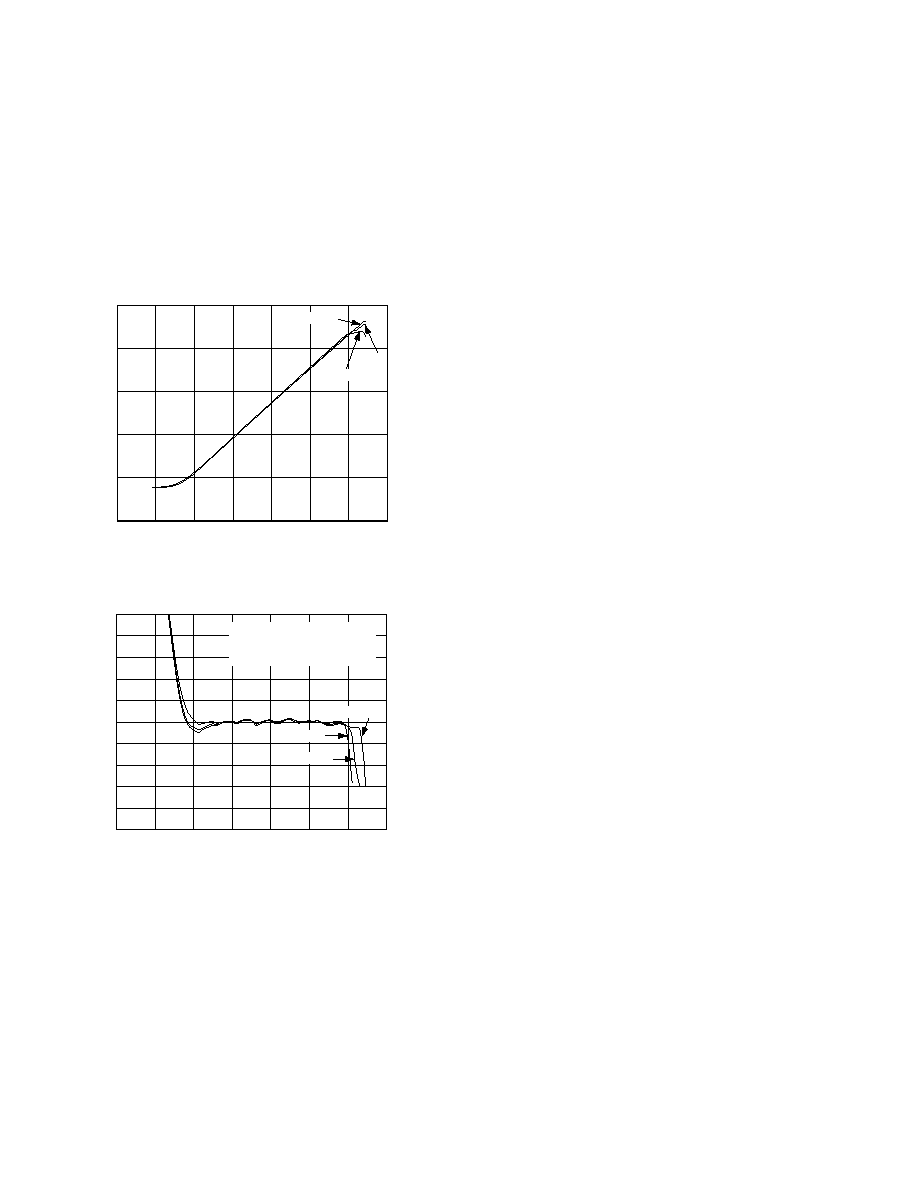

Figure 25 shows the output versus the input level in dBV, for

sine inputs at 10 MHz, 50 MHz and 100 MHz (add 13 to the

dBV number to get dBm Re 50

. Figure 26 shows the typi-

cal logarithmic linearity (log conformance) under the same

conditions.

INPUT LEVEL – dBV

2.5

–120

RSSI

OUTPUT

–

V

2

1.5

1

0.5

0

–100

–80

–60

–40

–20

0

20

100MHz

50MHz

10MHz

Figure 25. RSSI Output vs. Input Level at TA = +25°C for

Frequencies of 10 MHz, 50 MHz and 100 MHz

5

–120

ERROR

–

dB

4

3

2

1

0

–1

–2

–100

–80

–60

–40

–20

20

–3

–4

–5

–100

INPUT LEVEL – dBV

0

DYNAMIC RANGE

1dB

3dB

10MHz

86

93

50MHz

90

97

100MHz

96

100

100MHz

50MHz

10MHz

Figure 26. Log Linearity vs. Input Level at TA = +25°C, for

Frequencies of 10 MHz, 50 MHz and 100 MHz

Transfer Function in Terms of Slope and Intercept

The transfer function of the AD8306 is characterized in terms

of its Slope and Intercept. The logarithmic slope is defined as

the change in the RSSI output voltage for a 1 dB change at the

input. For the AD8306 the slope is calibrated to be 20 mV/dB.

The intercept is the point at which the extrapolated linear re-

sponse would intersect the horizontal axis. For the AD8306 the

intercept is calibrated to be –108 dBV (–95 dBm). Using the

slope and intercept, the output voltage can be calculated for any

input level within the specified input range using the equation:

VOUT = VSLOPE × (PIN – PO)

(2)

where VOUT is the demodulated and filtered RSSI output,

VSLOPE is the logarithmic slope, expressed in V/dB, PIN is the

input signal, expressed in decibels relative to some reference

level (either dBm or dBV in this case) and PO is the logarithmic

intercept, expressed in decibels relative to the same reference

level.

For example, for an input level of –33 dBV (–20 dBm), the

output voltage will be

VOUT = 0.02 V/dB × (–33 dBV – (–108 dBV)) = 1.5 V

(3)

The most widely used convention in RF systems is to specify

power in dBm, that is, decibels above 1 mW in 50

. Specifica-

tion of log amp input level in terms of power is strictly a conces-

sion to popular convention; they do not respond to power (tacitly

“power absorbed at the input”), but to the input voltage. The

use of dBV, defined as decibels with respect to a 1 V rms sine wave,

is more precise, although this is still not unambiguous because

waveform is also involved in the response of a log amp, which,

for a complex input (such as a CDMA signal) will not follow the

rms value exactly. Since most users specify RF signals in terms

of power—more specifically, in dBm/50

—we use both dBV

and dBm in specifying the performance of the AD8306, showing

equivalent dBm levels for the special case of a 50

environment.

Values in dBV are converted to dBm re 50

by adding 13.

Output Response Time and CF

The RSSI output has a low-pass corner frequency of 3.5 MHz,

which results in a 10% to 90% rise time of 73 ns. For low fre-

quency applications, the corner frequency can be reduced by

adding an external capacitor, CF, between FLTR (Pin 10) and

VLOG (Pin 16) as shown in Figure 24. For example, an exter-

nal 33 pF will reduce the corner frequency to 350 kHz, while

360 pF will set it to 35 kHz, in each case with an essentially

one-pole response.

Using the Limiter

Figure 27 shows the basic connections for operating the limiter

and the log output concurrently. The limiter output is a pair of

differential currents of magnitude, IOUT, from high impedance

(open-collector) sources. These are converted to equal-amplitude

voltages by supply-referenced load resistors, RLOAD. The limiter

output current is set by RLIM, the resistor connected between

Pin 9 (LMDR) and ground. The limiter output current is set

according the equation:

IOUT = –400 mV/RLIM

(5)

and has an absolute accuracy of

±5%.

The supply referenced voltage on each of the limiter pins will

thus be given by:

VLIM = VS –400 mV × RLOAD/RLIM

(6)

相關PDF資料 |

PDF描述 |

|---|---|

| 5962-9959101QPA | 3-CHANNEL POWER SUPPLY SUPPORT CKT, CDIP8 |

| 5962-9959101Q2A | 3-CHANNEL POWER SUPPLY SUPPORT CKT, CQCC20 |

| 5962F0623701V9A | OP-AMP, 500 uV OFFSET-MAX, 7.5 MHz BAND WIDTH, UUC |

| 5962F0623701VXC | OP-AMP, 500 uV OFFSET-MAX, 7.5 MHz BAND WIDTH, CDFP8 |

| 5962F9553602VPA | OP-AMP, 7000 uV OFFSET-MAX, 200 MHz BAND WIDTH, CDIP8 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-9865101QFA | 功能描述:LVDS 接口集成電路 RoHS:否 制造商:Texas Instruments 激勵器數(shù)量:4 接收機數(shù)量:4 數(shù)據(jù)速率:155.5 Mbps 工作電源電壓:5 V 最大功率耗散:1025 mW 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-16 Narrow 封裝:Reel |

| 5962-9865101QXA | 制造商:Texas Instruments 功能描述: |

| 5962-9865201QFA | 功能描述:LVDS 接口集成電路 RoHS:否 制造商:Texas Instruments 激勵器數(shù)量:4 接收機數(shù)量:4 數(shù)據(jù)速率:155.5 Mbps 工作電源電壓:5 V 最大功率耗散:1025 mW 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-16 Narrow 封裝:Reel |

| 5962-9865501QJA | 制造商:Texas Instruments 功能描述:Latch/Decoder/Demultiplexer Single 4-to-16 24-Pin CDIP Tube |

| 5962-9865901HXA | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 65Msps 12-bit Parallel 68-Pin LCCC 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。