- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄164924 > 9701-11 (PEREGRINE SEMICONDUCTOR CORP) 3000 MHz UltraCMOS⑩ Integer-N PLL Rad Hard for Space Applications PDF資料下載

參數(shù)資料

| 型號(hào): | 9701-11 |

| 廠商: | PEREGRINE SEMICONDUCTOR CORP |

| 元件分類: | PLL合成/DDS/VCOs |

| 英文描述: | 3000 MHz UltraCMOS⑩ Integer-N PLL Rad Hard for Space Applications |

| 中文描述: | PHASE LOCKED LOOP, CQCC44 |

| 封裝: | CERAMIC, QFJ-44 |

| 文件頁數(shù): | 13/13頁 |

| 文件大小: | 280K |

| 代理商: | 9701-11 |

Product Specification

PE9701

Page 9 of 13

Document No. 70-0035-02

│ www.psemi.com

2003-2006 Peregrine Semiconductor Corp. All rights reserved.

Serial Interface Mode

Serial Interface Mode is selected by setting the

Bmode input “l(fā)ow” and the Smode input “high”.

While the E_WR input is “l(fā)ow” and the S_WR

input is “l(fā)ow”, serial input data (Sdata input), B0 to

B19, is clocked serially into the primary register on

the rising edge of Sclk, MSB (B0) first.

The

contents from the primary register are transferred

into the secondary register on the rising edge of

either S_WR or Hop_WR according to the timing

diagram shown in Figure 6. Data is transferred to

the counters as shown in Table 7 on page 9.

The double buffering provided by the primary and

secondary registers allows for “ping-pong” counter

control using the FSELS input. When FSELS is

“high”, the primary register contents set the

counter inputs.

When FSELS is “l(fā)ow”, the

secondary register contents are utilized.

While the E_WR input is “high” and the S_WR

input is “l(fā)ow”, serial input data (Sdata input), B0 to

B7, is clocked serially into the enhancement

register on the rising edge of Sclk, MSB (B0) first.

The enhancement register is double buffered to

prevent inadvertent control changes during serial

loading, with buffer capture of the serially-entered

data performed on the falling edge of E_WR

according to the timing diagram shown in Figure

6. After the falling edge of E_WR, the data

provides control bits as shown in Table 8 with bit

functionality enabled by asserting the

Enh input

“l(fā)ow”.

Direct Interface Mode

Direct Interface Mode is selected by setting the

Bmode input “high”.

Counter control bits are set directly at the pins as

shown in Table 7. In Direct Interface Mode, main

counter inputs M7 and M8, and R Counter inputs

R4 and R5 are internally forced low (“0”).

MSB (first in)

(last in) LSB

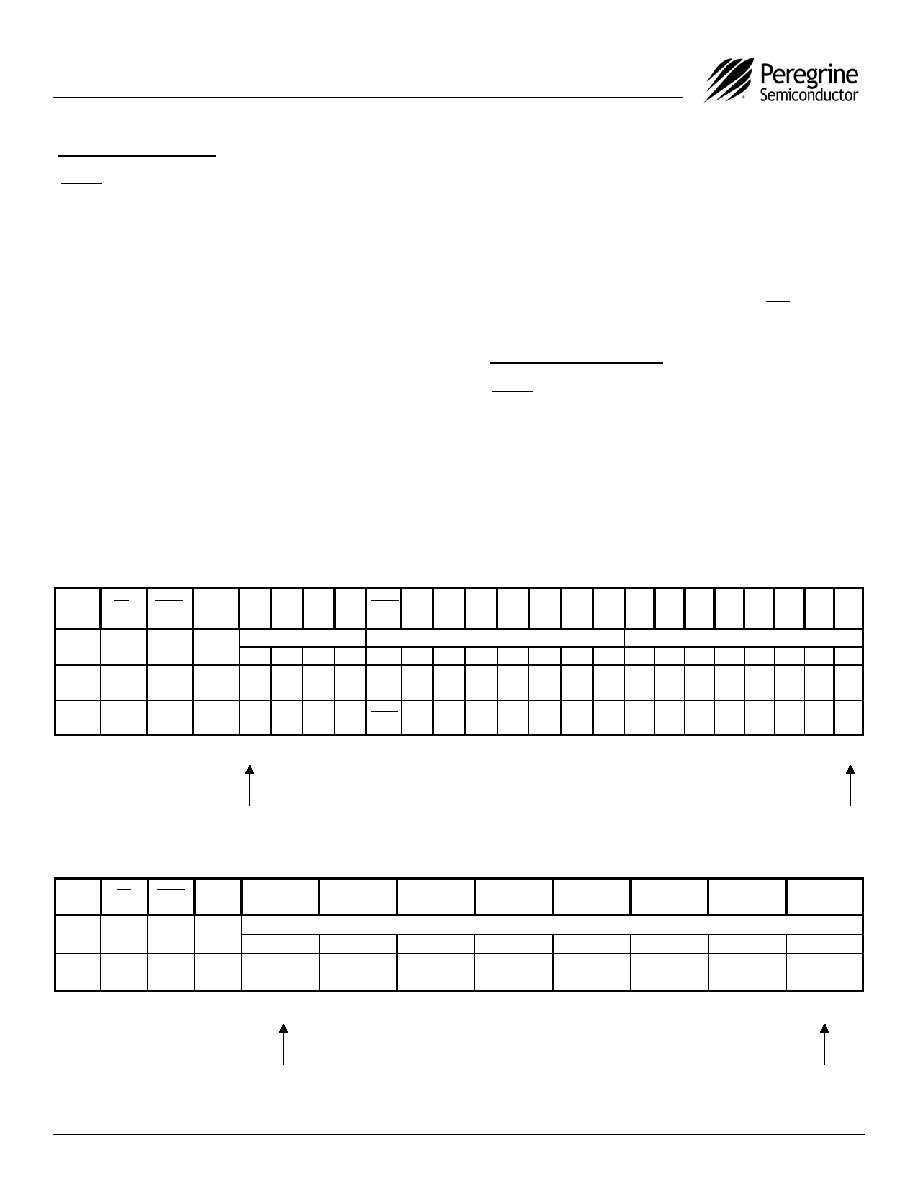

Table 7. Primary Register Programming

Table 8. Enhancement Register Programming

*Serial data clocked serially on Sclk rising edge while E_WR “l(fā)ow” and captured in secondary register on S_WR rising edge.

*Serial data clocked serially on Sclk rising edge while E_WR “high” and captured in the double buffer on E_WR falling edge.

MSB (first in)

(last in) LSB

Interface

Mode

Enh

Bmode

Smode

R5

R4

M8

M7

Pre_en

M6

M5

M4

M3

M2

M1

M0

R3

R2

R1

R0

A3

A2

A1

A0

Parallel

1

0

M2_WR rising edge load

M1_WR rising edge load

A_WR rising edge load

D3

D2

D1

D0

D7

D6

D5

D4

D3

D2

D1

D0

D7

D6

D5

D4

D3

D2

D1

D0

Serial*

1

0

1

B0

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

Direct

1

X

0

Pre_en

M6

M5

M4

M3

M2

M1

M0

R3

R2

R1

R0

A3

A2

A1

A0

Interface

Mode

Enh

Bmode

Smode

Reserved

Power

down

Counter

load

MSEL

output

Prescaler

output

fc, fp OE

Parallel

0

E_WR rising edge load

D7

D6

D5

D4

D3

D2

D1

D0

Serial*

0

1

B0

B1

B2

B3

B4

B5

B6

B7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9702-01 | 3.0 GHz Integer-N PLL for Rad Hard Applications |

| 9702-11 | 3.0 GHz Integer-N PLL for Rad Hard Applications |

| 9704-01 | 3.0 GHz Integer-N PLL for Rad Hard Apllications |

| 9704-11 | 3.0 GHz Integer-N PLL for Rad Hard Apllications |

| 971-36006-21 | 36 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, PRESS FIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 97011102 | 制造商:Laird Technologies Inc 功能描述:CSTR STR BF |

| 97011-1024-00-0 | 制造商:Kontron 功能描述:DDR2 SO-DIMM MEMORY MODULE WITH 1GB (667MHZ) - Bulk |

| 97011-1024-00-1 | 制造商:Kontron 功能描述:DDR2-SODIMM 1024MB PC2-5300 E1 - Bulk |

| 97011-1024-00-8 | 制造商:Kontron 功能描述:97011-1024-00-8 - Bulk |

| 97011-1024-00-9 | 制造商:Kontron 功能描述:DDR2-SODIMM 1024MB PC2-4200 E2 - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。