- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄164924 > 9701-11 (PEREGRINE SEMICONDUCTOR CORP) 3000 MHz UltraCMOS⑩ Integer-N PLL Rad Hard for Space Applications PDF資料下載

參數(shù)資料

| 型號(hào): | 9701-11 |

| 廠商: | PEREGRINE SEMICONDUCTOR CORP |

| 元件分類: | PLL合成/DDS/VCOs |

| 英文描述: | 3000 MHz UltraCMOS⑩ Integer-N PLL Rad Hard for Space Applications |

| 中文描述: | PHASE LOCKED LOOP, CQCC44 |

| 封裝: | CERAMIC, QFJ-44 |

| 文件頁數(shù): | 3/13頁 |

| 文件大小: | 280K |

| 代理商: | 9701-11 |

Product Specification

PE9701

Page 11 of 13

Document No. 70-0035-02

│ www.psemi.com

2003-2006 Peregrine Semiconductor Corp. All rights reserved.

pin CP. The current pulses from pin CP are low

pass filtered externally and then connected to the

VCO tune voltage. PD_U pulses result in a

current source, which increases the VCO

frequency; PD_D pulses result in a current sink,

which decreases VCO frequency.

A lock detect output, LD is also provided, via the

pin Cext. Cext is the logical “NAND” of PD_U and

PD_D waveforms, which is driven through a series

2k

resistor. Connecting Cext to an external

shunt capacitor provides integration. Cext also

drives the input of an internal inverting comparator

with an open drain output. Thus LD is an “AND”

function of PD_U and PD_D. See Figure 4 for a

schematic of this circuit.

Enhancement Register

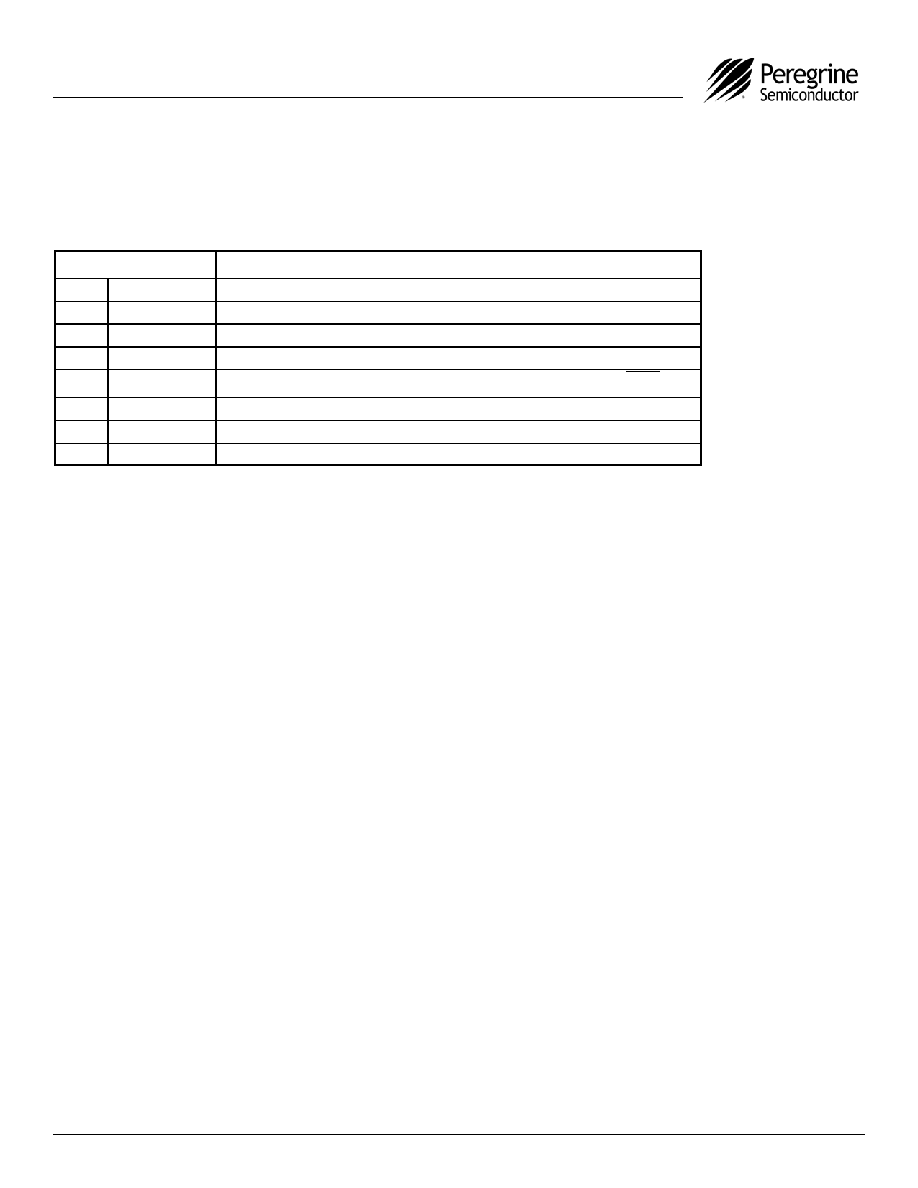

The functions of the enhancement register bits are shown below with all bits active “high”.

Table 9. Enhancement Register Bit Functionality

** Program to 0

Phase Detector

The phase detector is triggered by rising edges

from the main Counter (fp) and the reference

counter (fc). It has two outputs, namely PD_U,

and PD_D. If the divided VCO leads the divided

reference in phase or frequency (fp leads fc),

PD_D pulses “high”. If the divided reference leads

the divided VCO in phase or frequency (fr leads

fp), PD_U pulses “high”. The width of either pulse

is directly proportional to phase offset between the

two input signals, fp and fc.

The signals from the phase detector couple

directly to a charge pump. PD_U controls a

current source at pin CP with constant amplitude

and pulse duration approximately the same as

PD_U. PD_D similarly drives a current sink at

Bit Function

Description

Bit 0

Reserved**

Bit 1

Reserved**

Bit 2

Reserved**

Bit 3

Power down

Power down of all functions except programming interface.

Bit 4

Counter load

Immediate and continuous load of counter programming as directed by the

Bmode and

Smode inputs.

Bit 5

MSEL output

Drives the internal dual modulus prescaler modulus select (MSEL) onto the Dout output.

Bit 6

Prescaler output

Drives the raw internal prescaler output (fmain) onto the Dout output.

Bit 7

fp, fc OE

fp, fc outputs disabled.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9702-01 | 3.0 GHz Integer-N PLL for Rad Hard Applications |

| 9702-11 | 3.0 GHz Integer-N PLL for Rad Hard Applications |

| 9704-01 | 3.0 GHz Integer-N PLL for Rad Hard Apllications |

| 9704-11 | 3.0 GHz Integer-N PLL for Rad Hard Apllications |

| 971-36006-21 | 36 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, PRESS FIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 97011102 | 制造商:Laird Technologies Inc 功能描述:CSTR STR BF |

| 97011-1024-00-0 | 制造商:Kontron 功能描述:DDR2 SO-DIMM MEMORY MODULE WITH 1GB (667MHZ) - Bulk |

| 97011-1024-00-1 | 制造商:Kontron 功能描述:DDR2-SODIMM 1024MB PC2-5300 E1 - Bulk |

| 97011-1024-00-8 | 制造商:Kontron 功能描述:97011-1024-00-8 - Bulk |

| 97011-1024-00-9 | 制造商:Kontron 功能描述:DDR2-SODIMM 1024MB PC2-4200 E2 - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。