- 您現在的位置:買賣IC網 > PDF目錄373911 > AD7641BCPZ (ANALOG DEVICES INC) 18-Bit 250/670 kSPS PulSAR Bipolar Programmable Inputs ADC PDF資料下載

參數資料

| 型號: | AD7641BCPZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 18-Bit 250/670 kSPS PulSAR Bipolar Programmable Inputs ADC |

| 中文描述: | 1-CH 18-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, QCC48 |

| 封裝: | 7 X 7 MM, LEAD FREE, MO-220VKKD-2, LFCSP-48 |

| 文件頁數: | 11/14頁 |

| 文件大小: | 192K |

| 代理商: | AD7641BCPZ |

Preliminary Technical Data

AD7631/AD7634

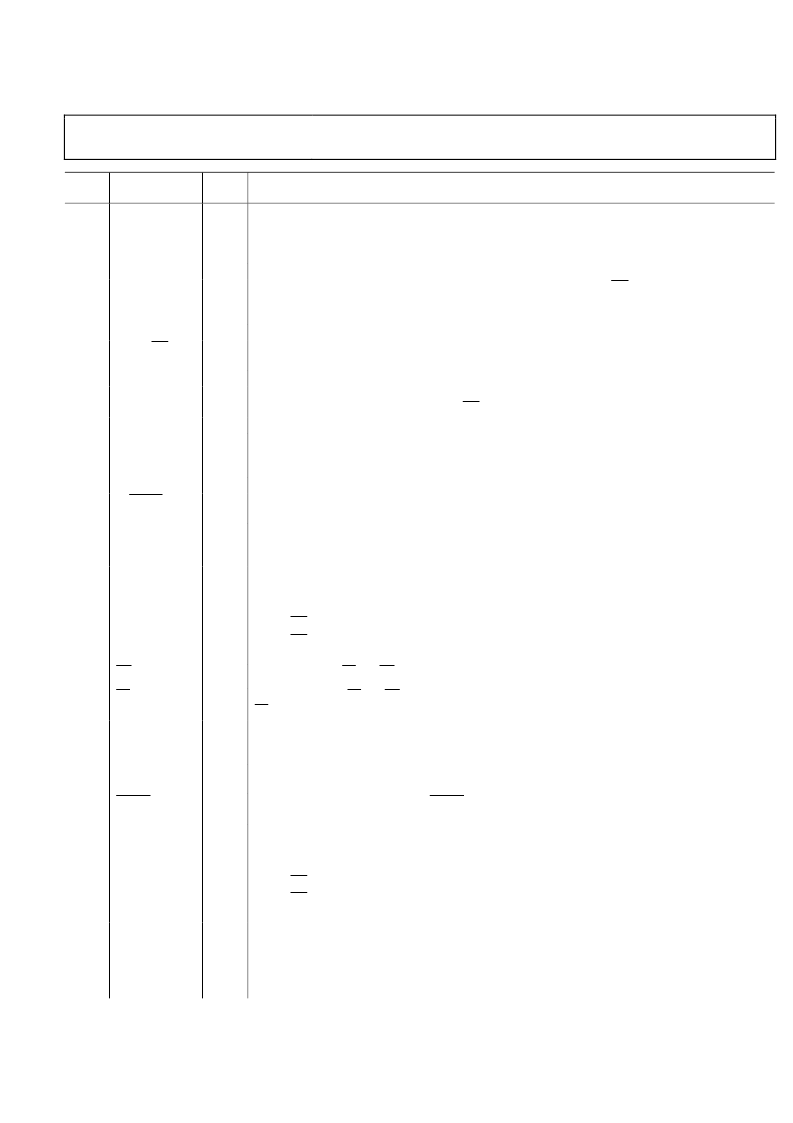

Pin

No.

Rev. PrC | Page 11 of 14

Mnemonic

Type

1

Description

When a read sequence is initiated and INVSYNC = low, SYNC is driven high and remains high

while SDOUT output is valid.

When a read sequence is initiated and INVSYNC = high, SYNC is driven low and remains low

while SDOUT output is valid.

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 13 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode), read error. In serial slave mode (EXT/INT = high), this output

is used as an incomplete read error flag. If a data read is started and not completed when the

current conversion is complete, the current data is lost and RDERROR is pulsed high.

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 14 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode) hardware/software select. This input, part of the serial

programmable port, is used to select hardware or software input ranges and mode selection.

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 15 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode), serial programmable port data. This input is used to write in the

serial programmable port data when HW/SW = low.

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 16 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode), serial programmable port clock. This input is used to clock in the

data on SPPDATA. The active edge where the data SPPDATA is updated depends on the logic state of

the INVSCLK pin.

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 17 of the parallel port data output bus.

When MODE[1:0] = 3 (serial mode), serial programmable port enable. Asserting this input enables the

serial programmable port.

Busy Output. Transitions high when a conversion is started and remains high until the conversion

is complete and the data is latched into the on-chip shift register. The falling edge of BUSY can be

used as a data-ready clock signal.

10 Volt Input Range. Refer to Table 8.

When MODE[1:0] = 0, 1, or 2, this input is used to select the 10V input range.

When MODE[1:0] = 3 (serial mode), and

HW/SW = high, driving TEN high selects the 10 Volt input range.

HW/SW = low, the input range is programmed with the serial programmable port and this pin is a

don’t care.

Read Data. When CS and RD are both low, the interface parallel or serial output bus is enabled.

24

D13

or RDERROR

DO

25

D14

or HW/SW

DI/O

26

D15

or SPPDATA

DI/O

27

D16

or SPPCLK

DI/O

28

D17

or SPPEN

DI/O

29

BUSY

DO

30

TEN

DI

31

RD

DI

32

CS

DI

Chip Select. When CS and RD are both low, the interface parallel or serial output bus is enabled.

CS is also used to gate the external clock in slave serial mode.

Reset Input. When high, resets the ADC. Current conversion, if any, is aborted. Falling edge of

RESET enables the calibration mode indicated by pulsing BUSY high. If not used, this pin can be tied to

DGND.

Power-Down Input. When high, power downs the ADC. Power consumption is reduced and

conversions are inhibited after the current one is completed.

Conversion Start. A falling edge on CNVST puts the internal sample-and-hold into the hold state

and initiates a conversion.

Bipolar Input Range. Refer to Table 8.

When MODE[1:0] = 0, 1, or 2, this input is used to select the bipolar input range.

When MODE[1:0] = 3 (serial mode), and

HW/SW = high, driving BIP high selects the bipolar input range.

HW/SW = low, the input range is programmed with the serial programmable port and this pin is a

don’t care.

Reference Output/Input.

When PDREF/PDBUF = low, the internal reference and buffer are enabled producing 5 V on this pin.

When PDREF/PDBUF = high, the internal reference and buffer are disabled allowing an externally

supplied voltage reference up to AVDD volts. Decoupling is required with or without the internal

reference and buffer.

33

RESET

DI

34

PD

DI

35

CNVST

DI

36

BIP

DI

37

REF

AI/O

相關PDF資料 |

PDF描述 |

|---|---|

| AD7641BCPZRL | 18-Bit 250/670 kSPS PulSAR Bipolar Programmable Inputs ADC |

| AD7641BSTZ | 18-Bit 250/670 kSPS PulSAR Bipolar Programmable Inputs ADC |

| AD7641BSTZRL | 18-Bit 250/670 kSPS PulSAR Bipolar Programmable Inputs ADC |

| AD7641 | 18-Bit, 2 MSPS SAR ADC |

| AD7641ACP | 18-Bit, 2 MSPS SAR ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7641BCPZRL | 功能描述:IC ADC 18BIT 2MSPS SAR 48-LFCSP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7641BSTZ | 功能描述:IC ADC 18BIT 2MSPS SAR 48-LQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:microPOWER™ 位數:8 采樣率(每秒):1M 數據接口:串行,SPI? 轉換器數目:1 功率耗散(最大):- 電壓電源:模擬和數字 工作溫度:-40°C ~ 125°C 安裝類型:表面貼裝 封裝/外殼:24-VFQFN 裸露焊盤 供應商設備封裝:24-VQFN 裸露焊盤(4x4) 包裝:Digi-Reel® 輸入數目和類型:8 個單端,單極 產品目錄頁面:892 (CN2011-ZH PDF) 其它名稱:296-25851-6 |

| AD7641BSTZRL | 功能描述:IC ADC 18BIT 2MSPS SAR 48-LQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7641XST | 制造商:Analog Devices 功能描述: |

| AD7641XST-U3 | 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。