- 您現在的位置:買賣IC網 > PDF目錄373925 > AD7896JR (ANALOG DEVICES INC) 2.7 V to 5.5 V, 12-Bit, 8 us ADC in 8-Pin SO/DIP PDF資料下載

參數資料

| 型號: | AD7896JR |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 2.7 V to 5.5 V, 12-Bit, 8 us ADC in 8-Pin SO/DIP |

| 中文描述: | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| 封裝: | MS-012AA, SOIC-8 |

| 文件頁數: | 7/12頁 |

| 文件大小: | 367K |

| 代理商: | AD7896JR |

AD7896

REV. B

–7–

OPERATING MODES

Mode 1 Operation (High Sampling Performance)

The timing diagram in Figure 2 is for optimum performance in

Operating Mode 1 where the falling edge of

CONVST

starts

conversion and puts the Track/Hold amplifier into its hold

mode. This falling edge of

CONVST

also causes the BUSY sig-

nal to go high to indicate that a conversion is taking place. The

BUSY signal goes low when the conversion is complete which is

8

μ

s max after the falling edge of

CONVST,

and new data from

this conversion is available in the output register of the AD7896.

A read operation accesses this data. This read operation consists

of 16 clock cycles, and the length of this read operation will de-

pend on the serial clock frequency. For the fastest throughput

rate (with a serial clock of 10 MHz 5 V operation) the read op-

eration will take 1.6

μ

s. The read operation must be complete at

least 400 ns before the falling edge of the next

CONVST,

and

this gives a total time of 10

μ

s for the full throughput time

(equivalent to 100 kHz). This mode of operation should be used

for high sampling applications.

14

μ

s shown in diagram from the rising edge of

CONVST

. This

is because the Track/Hold amplifier goes into its hold mode on

the falling edge of

CONVST

and then the conversion will not be

complete for a further 8

μ

s. In this case the BUSY will be the

best indicator for when the conversion is complete. Even though

the part is in sleep mode, data can still be read from the part.

The read operation consists of 16 clock cycles as in Mode 1 op-

eration. For the fastest serial clock of 10 MHz 5 V operation the

read operation will take 1.6

μ

s, and this must be complete at

least 400 ns before the falling edge of the next

CONVST

to al-

low the Track/Hold amplifier to have enough time to settle.

This mode is very useful when the part is converting at a slow

rate as the power consumption will be significantly reduced

from that of Mode 1 operation.

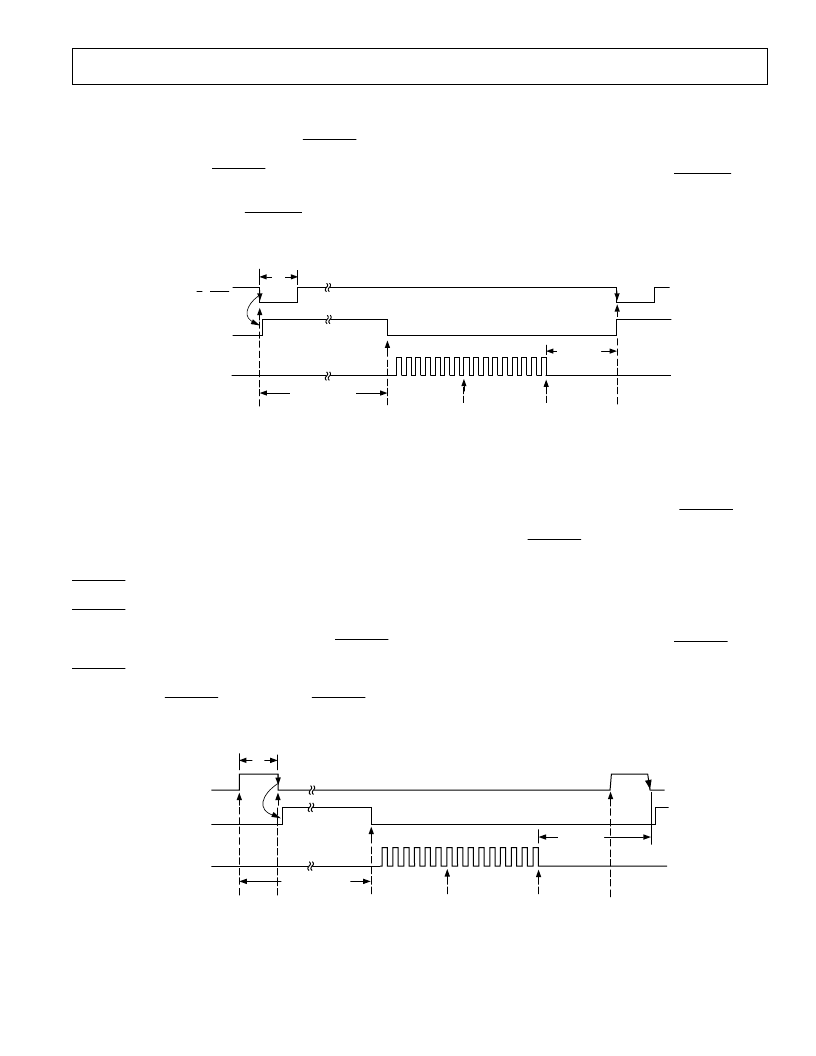

Mode 2 Operation (Auto Sleep After Conversion)

The timing diagram in Figure 3 is for optimum performance in

Operating Mode 2 where the part automatically goes into sleep

mode once BUSY goes low after conversion and “wakes up” be-

fore the next conversion takes place. This is achieved by keeping

CONVST

low at the end of conversion whereas it was high at

the end of conversion for Mode 1 operation. The rising edge of

CONVST

“wakes up” the part. This wake-up time is 6

μ

s at

which point the Track/Hold amplifier goes into its hold mode.

The conversion takes 8

μ

s after this, provided the

CONVST

has gone low, giving a total of 14

μ

s from the rising edge of

CONVST

to the conversion being complete which is indicated

by the BUSY going low. Note that since the wake-up time from

the rising edge of

CONVST

is 6

μ

s, when the

CONVST

pulse

width is greater than 6

μ

s the conversion will take more than the

t

CONVERT

= 8μs

CONVST

BUSY

SCLK

SERIAL READ

OPERATION

CONVERSION ENDS

8μs LATER

OUTPUT

SERIAL

SHIFT

REGISTER

IS RESET

CONVERSION IS

INITIATED AND

TRACK/HOLD GOES INTO

HOLD

t

1

= 40ns MIN

400ns MIN

t

1

t

CONVERT

= 8μs

READ OPERATION

SHOULD END 400ns

PRIOR TO NEXT

FALLING EDGE OF

CONVST

Figure 2. Mode 1 Timing Operation Diagram for High Sampling Performance

CONVST

BUSY

SCLK

SERIAL READ

OPERATION

CONVERSION

ENDS

14μs LATER

READ OPERATION

SHOULD END 400ns

PRIOR TO NEXT

FALLING EDGE OF

CONVST

OUTPUT

SERIAL

SHIFT

REGISTER

IS RESET

PART

WAKES

UP

CONVERSION

IS INITIATED

TRACK/HOLD

GOES INTO

HOLD

t

1

= 6μs

WAKE-UP

TIME

t

1

t

CONVERT

= 14μs

400ns MIN

Figure 3. Mode 2 Timing Diagram Where Automatic Sleep Function Is Initiated

相關PDF資料 |

PDF描述 |

|---|---|

| AD7896 | 2.7 V to 5.5 V, 12-Bit, 8 us ADC in 8-Pin SO/DIP |

| AD7896AN | 14-Bit 50 kSPS ADC Ser. Out, 1.8V Operation 8-MSOP |

| AD7896AR | 2.7 V to 5.5 V, 12-Bit, 8 us ADC in 8-Pin SO/DIP |

| AD7896BN | 2.7 V to 5.5 V, 12-Bit, 8 us ADC in 8-Pin SO/DIP |

| AD7896BR | 2.7 V to 5.5 V, 12-Bit, 8 us ADC in 8-Pin SO/DIP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7896JR-REEL | 制造商:Analog Devices 功能描述:ADC Single SAR 100ksps 12-bit Serial 8-Pin SOIC N T/R 制造商:Analog Devices 功能描述:ADC SGL SAR 100KSPS 12-BIT SERL 8SOIC N - Tape and Reel 制造商:Rochester Electronics LLC 功能描述:12-BIT SAMPLING A/D IC - Tape and Reel |

| AD7896JRZ | 功能描述:IC ADC 12BIT SRL T/H HS 8SOIC RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 其它有關文件:TSA1204 View All Specifications 標準包裝:1 系列:- 位數:12 采樣率(每秒):20M 數據接口:并聯 轉換器數目:2 功率耗散(最大):155mW 電壓電源:模擬和數字 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-TQFP 供應商設備封裝:48-TQFP(7x7) 包裝:Digi-Reel® 輸入數目和類型:4 個單端,單極;2 個差分,單極 產品目錄頁面:1156 (CN2011-ZH PDF) 其它名稱:497-5435-6 |

| AD7896JRZ-REEL | 功能描述:IC ADC 12BIT SRL T/H HS 8SOIC RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:16 采樣率(每秒):45k 數據接口:串行 轉換器數目:2 功率耗散(最大):315mW 電壓電源:模擬和數字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數目和類型:2 個單端,單極 |

| AD7896SQ | 制造商:Rochester Electronics LLC 功能描述:12-BIT SAMPLING A/D IC - Bulk |

| AD7898AR10 | 制造商:AD 功能描述:New |

發布緊急采購,3分鐘左右您將得到回復。