- 您現在的位置:買賣IC網 > PDF目錄373929 > AD8019ARU (ANALOG DEVICES INC) DSL Line Driver with Power-Down PDF資料下載

參數資料

| 型號: | AD8019ARU |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通用總線功能 |

| 英文描述: | DSL Line Driver with Power-Down |

| 中文描述: | DUAL LINE DRIVER, PDSO14 |

| 封裝: | TSSOP-14 |

| 文件頁數: | 12/20頁 |

| 文件大小: | 782K |

| 代理商: | AD8019ARU |

REV. 0

AD8019

–12–

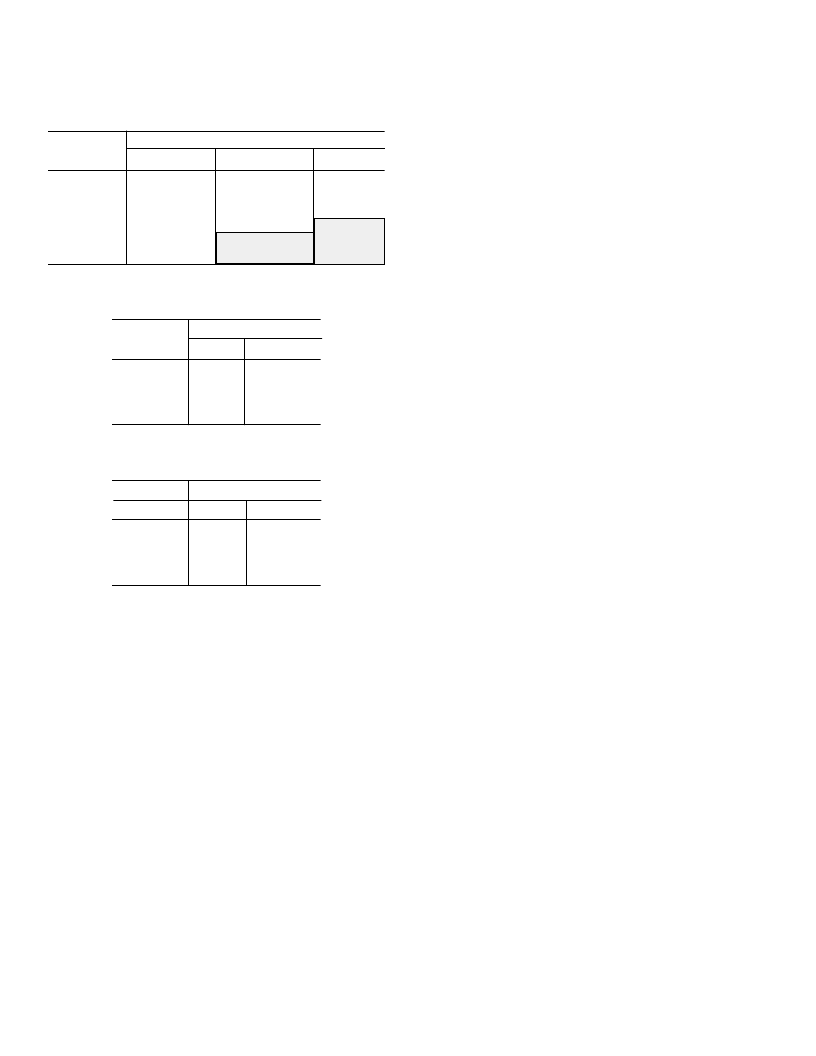

Table II. Junction Temperature vs. Line Power and Operating

Voltage for SOIC

V

SUPPLY

12

137

140

142

145

147

150

P

LINE

, dBm

13

14

15

16

17

18

12.5

140

142

145

148

150

153

13

143

145

148

151

154

157

Table III. Junction Temperature vs. Line Power and

Operating Voltage for TSSOP

V

SUPPLY

+12

P

LINE

, dBm

13

14

15

16

+13

115

116

118

120

118

119

121

123

Table IV. Junction Temperature vs. Line Power and

Operating Voltage for SOIC

V

SUPPLY

+12

P

LINE

, dBm

13

14

15

16

+13

118

120

122

124

121

123

125

128

Thermal stitching, which connects the outer layers to the inter-

nal ground plane(s), can help to utilize the thermal mass of the

PCB to draw heat away from the line driver and other active

components.

LAYOUT CONSIDERATIONS

As is the case with all high-speed applications, careful attention

to printed circuit board layout details will prevent associated

board parasitics from becoming problematic. Proper RF design

technique is mandatory. The PCB should have a ground plane

covering all unused portions of the component side of the board

to provide a low-impedance return path. Removing the ground

plane on all layers from the areas near the input and output pins

will reduce stray capacitance, particularly in the area of the

inverting inputs. The signal routing should be short and direct

in order to minimize parasitic inductance and capacitance asso-

ciated with these traces. Termination resistors and loads should

be located as close as possible to their respective inputs and

outputs. Input and output traces should be kept as far apart as

possible to minimize coupling (crosstalk) though the board.

Wherever there are complementary signals, a symmetrical

layout should be provided to the extent possible to maximize

balanced performance. When running differential signals over a

long distance, the traces on the PCB should be close together or

any differential wiring should be twisted together to minimize

the area of the loop that is formed. This will reduce the radiated

energy and make the circuit less susceptible to RF interference.

Adherence to stripline design techniques for long signal traces

(greater than about 1 inch) is recommended.

Evaluation Board

The AD8019 is available installed on an evaluation board for

both package styles. Figures 8 and 9 show the schematics for the

TSSOP evaluation board.

The receiver circuit on these boards is typically unpopulated.

Requesting samples of the AD8022AR, along with either of the

AD8019 evaluation boards, will provide the capability to evaluate

the AD8019 along with other Analog Devices products in a typical

transceiver circuit. The evaluation circuits have been designed

to replicate the CPE side analog transceiver hybrid circuits.

The circuit mentioned above is designed using a 1-transformer

transceiver topology including a line receiver, line driver, line

matching network, an RJ11 jack for interfacing to line simula-

tors, and differential inputs.

AC-coupling capacitors of 0.1

μ

F, C8, and C10, in combination

with 10 k

, resistors R24 and R25, will form a 1st order high-

pass pole at 160 Hz.

Transformer Selection

Customer premise ADSL requires the transmission of a 13 dBm

(20 mW) DMT signal. The DMT signal has a crest factor of 5.3,

requiring the line driver to provide peak line power of 560 mW.

560 mW peak line power translates into a 7.5 V peak voltage on

a 100

telephone line. Assuming that the maximum low distor-

tion output swing available from the AD8019 line driver on a

±

12 V supply is 20 V and taking into account the power lost due

to the termination resistance, a step-up transformer with turns

ratio of 1:1 is adequate for most applications. If the modem

designer desires to transmit more than 13 dBm down the twisted

pair, a higher turns ratio can be used for the transformer. This

trade-off comes at the expense of higher power dissipation by

the line driver as well as increased attenuation of the downstream

signal that is received by the transceiver.

In the simplified differential drive circuit shown in Figure 7,

the AD8019 is coupled to the phone line through a step-up

transformer with a 1:1 turns ratio. R1 and R2 are back termi-

nation or line matching resistors, each 50

(100

/(2

×

1

2

))

where 100

is the approximate phone line impedance. A

transformer reflects impedance from the line side to the IC

side as a value inversely proportional to the square of the turns

ratio. The total differential load for the AD8019, including the

termination resistors, is 200

. Even under these conditions

the AD8019 provides low distortion signals to within 2 V of

the power supply rails.

One must take care to minimize any capacitance present at the

outputs of a line driver. The sources of such capacitance can

include, but are not limited to EMI suppression capacitors,

overvoltage protection devices and the transformers used in the

hybrid. Transformers have two kinds of parasitic capacitances,

distributed, or bulk capacitance, and interwinding capacitance.

Distributed capacitance is a result of the capacitance created

between each adjacent winding on a transformer. Interwinding

capacitance is the capacitance that exists between the windings

on the primary and secondary sides of the transformer. The

existence of these capacitances is unavoidable, but in specifying

相關PDF資料 |

PDF描述 |

|---|---|

| AD8019AR-EVAL | DSL Line Driver with Power-Down |

| AD8019AR-REEL | DSL Line Driver with Power-Down |

| AD802-155BR | Clock Recovery and Data Retiming Phase-Locked Loop |

| AD802-155KR | Clock Recovery and Data Retiming Phase-Locked Loop |

| AD8021 | Low Noise, High Speed Amplifier for 16-Bit Systems |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD8019ARU-EVAL | 制造商:Analog Devices 功能描述:Evaluation Board For DSL Line Driver With Power-Down |

| AD8019ARU-REEL | 制造商:Analog Devices 功能描述:ADSL Driver Dual 180MHz 14-Pin TSSOP T/R 制造商:Analog Devices 功能描述:ADSL DRVR DUAL 180MHZ 14TSSOP - Tape and Reel 制造商:Rochester Electronics LLC 功能描述:TSSOP DSL LINE DRIVER WITH POWER DOWN - Tape and Reel |

| AD8019ARUZ | 制造商:Analog Devices 功能描述:ADSL Driver Dual 180MHz 14-Pin TSSOP |

| AD8019ARZ | 制造商:Analog Devices 功能描述:ADSL Driver Dual 180MHz 8-Pin SOIC N |

| AD802 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:AD800/AD802: Clock Recovery and Data Retiming Phase-Locked Loop Data Sheet (Rev. B. 12/93) |

發布緊急采購,3分鐘左右您將得到回復。