- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373929 > AD8019ARU (ANALOG DEVICES INC) DSL Line Driver with Power-Down PDF資料下載

參數(shù)資料

| 型號: | AD8019ARU |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通用總線功能 |

| 英文描述: | DSL Line Driver with Power-Down |

| 中文描述: | DUAL LINE DRIVER, PDSO14 |

| 封裝: | TSSOP-14 |

| 文件頁數(shù): | 3/20頁 |

| 文件大小: | 782K |

| 代理商: | AD8019ARU |

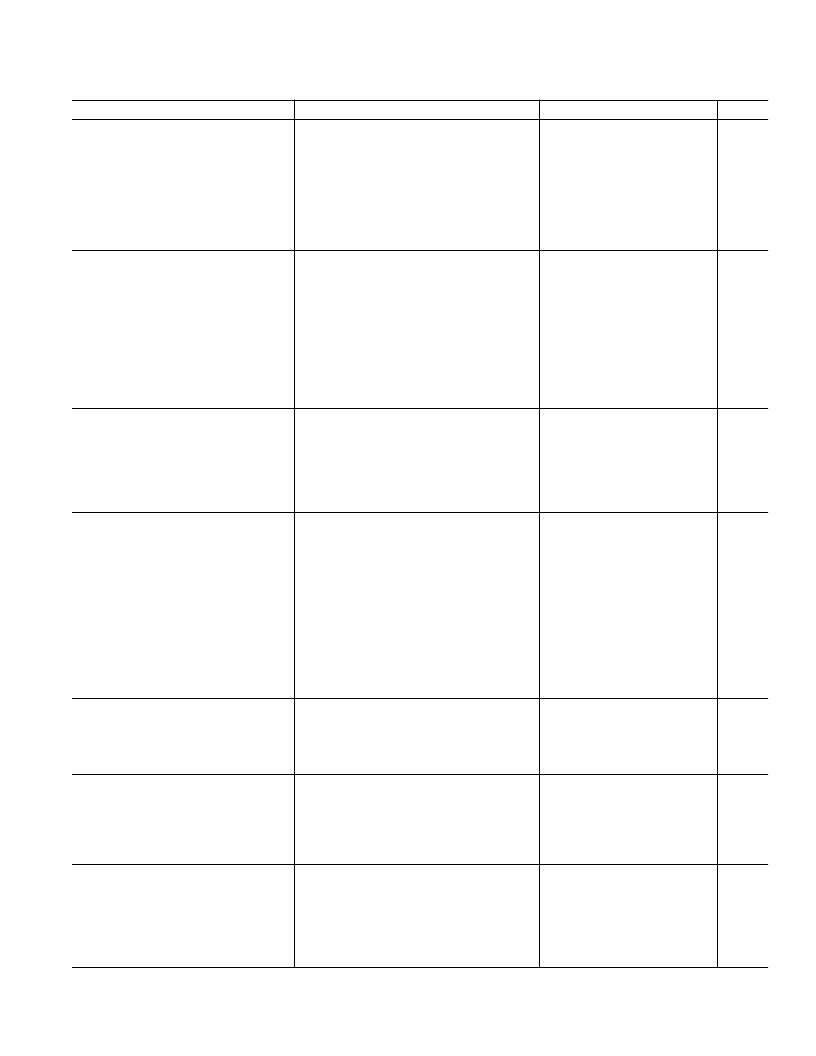

REV. 0

–3–

AD8019

Parameter

Conditions

Min

Typ

Max

Unit

DYNAMIC PERFORMANCE

–3 dB Bandwidth

G = +5

G = +1, V

OUT

< 0.4 V p-p

G = +2, V

OUT

< 0.4 V p-p

V

OUT

< 0.4 V p-p

V

OUT

= 4 V p-p

Noninverting, V

OUT

= 4 V p-p

Noninverting, V

OUT

= 2 V p-p

0.1%, V

OUT

= 2 V p-p

35

180

75

5.5

50

400

5.5

40

MHz

MHz

MHz

MHz

MHz

V/

μ

s

ns

ns

175

70

0.1 dB Bandwidth

Large Signal Bandwidth

Slew Rate

Rise and Fall Time

Settling Time

NOISE/DISTORTION PERFORMANCE

Distortion

Second Harmonic

V

OUT

= 16 V p-p (Differential)

100 kHz, R

L(DM)

= 200

500 kHz, R

L(DM)

= 200

100 kHz, R

L(DM)

= 200

500 kHz, R

L(DM)

= 200

144 kHz–500 kHz, Differential R

L

= 200

25 kHz–138 kHz, Differential R

L

= 200

f = 100 kHz

f = 100 kHz

f = 1 MHz, G = +2

–80

–72

–85

–80

–80

–73

8

0.9

–85

dBc

dBc

dBc

dBc

dBc

dBc

nV/

√

Hz

pA

√

Hz

dB

Third Harmonic

Out-of-Band SFDR

MTPR

Input Voltage Noise

Input Current Noise

Crosstalk

DC PERFORMANCE

Input Offset Voltage

5

10

1

2

92

90

20

mV

mV

mV

mV

dB

dB

T

MIN

–T

MAX

Input Offset Voltage Match

12

18

T

MIN

–T

MAX

V

OUT

= 18 V p-p, R

L

= 100

T

MIN

–T

MAX

Open-Loop Gain

86

INPUT CHARACTERISTICS

Input Resistance

Input Capacitance

+Input Bias Current

10

0.5

–0.5

M

pF

μ

A

μ

A

μ

A

μ

A

μ

A

μ

A

μ

A

μ

A

dB

V

–3

–3.8

–1.5

–1.7

–1.0

–2.4

–1.0

–2.5

71

–10

+3

+3.8

+1.5

+1.7

+1.0

+2.4

+1.0

+2.5

T

MIN

–T

MAX

–Input Bias Current

–0.2

T

MIN

–T

MAX

+Input Bias Current Match

+0.2

T

MIN

–T

MAX

–Input Bias Current Match

+0.1

T

MIN

–T

MAX

V

CM

= –10 V to +10 V

CMRR

Input CM Voltage Range

76

+10

OUTPUT CHARACTERISTICS

Output Resistance

Output Voltage Swing

Output Current

Short Circuit Current

1

0.2

V

mA

mA

R

L

= 100

SFDR –80 dBc into 100

at 100 kHz

–10.8

125

+10.8

170

800

POWER SUPPLY

Supply Current/Amp

PWDN = High

T

MIN

–T

MAX

PWDN = Low

Dual Supply

±

V

S

= +1.0 V to –1.0 V

9

10

11.5

1.75

±

12

mA

mA

mA

V

dB

0.8

Operating Range

Power Supply Rejection Ratio

±

4.0

61

64

LOGIC LEVELS

t

ON

t

OFF

PWDN = “1” Voltage

PWDN = “0” Voltage

PWDN = “1” Bias Current

PWDN = “0” Bias Current

V

PWDN

= 0 V to 3 V; V

IN

= 10 MHz, G = +5

120

80

ns

ns

V

V

μ

A

μ

A

1.8

+V

S

0.5

220

–100

NOTES

1

This device is protected from overheating during a short-circuit by a thermal shutdown circuit.

Specifications subject to change without notice.

(@ 25 C, V

S

= 12 V, R

L

= 100 , R

F

= 500 , T

MIN

= –40 C, T

MAX

= +85 C, unless otherwise noted.)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD8019AR-EVAL | DSL Line Driver with Power-Down |

| AD8019AR-REEL | DSL Line Driver with Power-Down |

| AD802-155BR | Clock Recovery and Data Retiming Phase-Locked Loop |

| AD802-155KR | Clock Recovery and Data Retiming Phase-Locked Loop |

| AD8021 | Low Noise, High Speed Amplifier for 16-Bit Systems |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD8019ARU-EVAL | 制造商:Analog Devices 功能描述:Evaluation Board For DSL Line Driver With Power-Down |

| AD8019ARU-REEL | 制造商:Analog Devices 功能描述:ADSL Driver Dual 180MHz 14-Pin TSSOP T/R 制造商:Analog Devices 功能描述:ADSL DRVR DUAL 180MHZ 14TSSOP - Tape and Reel 制造商:Rochester Electronics LLC 功能描述:TSSOP DSL LINE DRIVER WITH POWER DOWN - Tape and Reel |

| AD8019ARUZ | 制造商:Analog Devices 功能描述:ADSL Driver Dual 180MHz 14-Pin TSSOP |

| AD8019ARZ | 制造商:Analog Devices 功能描述:ADSL Driver Dual 180MHz 8-Pin SOIC N |

| AD802 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:AD800/AD802: Clock Recovery and Data Retiming Phase-Locked Loop Data Sheet (Rev. B. 12/93) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。