- 您現在的位置:買賣IC網 > PDF目錄373961 > AD9226 (Analog Devices, Inc.) Complete 12-Bit, 65 MSPS ADC Converter PDF資料下載

參數資料

| 型號: | AD9226 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Complete 12-Bit, 65 MSPS ADC Converter |

| 中文描述: | 完整的12位,65 MSPS的ADC轉換 |

| 文件頁數: | 21/28頁 |

| 文件大小: | 1480K |

| 代理商: | AD9226 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

REV. 0

AD9226

–21–

VR

VR is an internal bias point on the LQFP package. It must be

decoupled to ground with a 0.1

μ

F capacitor.

The digital activity on the AD9226 chip falls into two general

categories: correction logic and output drivers. The internal

correction logic draws relatively small surges of current, mainly

during the clock transitions. The output drivers draw large

current impulses while the output bits are changing. The size

and duration of these currents are a function of the load on the

output bits: large capacitive loads are to be avoided.

For the digital decoupling shown in Figure 19, 0.1

μ

F ceramic

chip and 10

μ

F tantalum capacitors are appropriate. Reason-

able capacitive loads on the data pins are less than 20 pF per

bit. Applications involving greater digital loads should consider

increasing the digital decoupling proportionally and/or using

external buffers/latches.

A complete decoupling scheme will also include large tantalum

or electrolytic capacitors on the power supply connector to

reduce low-frequency ripple to negligible levels.

EVALUATION BOARD AND TYPICAL BENCH

CHARACTERIZATION TEST SETUP

The AD9226 evaluation board is configured to operate upon

applying both power and the analog and clock input signals. It

provides three possible analog input interfaces to characterize

the AD9226

’

s ac and dc performance. For ac characterization, it

provides a transformer coupled input with the common-mode

input voltage (CMV) set to AVDD/2. Note, the evaluation

board is shipped with a transformer coupled interface and a 2 V

input span. For differential dc coupled applications, the evalua-

tion board has provisions to be driven by the AD8138 amplifier.

If a single-ended input is desired, it may be driven through the

S3 connector. The various input signal options are accessible by

the jumper connections. Refer to the Evaluation Board schematic.

The clock input signal to the AD9226 evaluation board can be

applied to one of two inputs, CLOCK and AUXCLK. The

CLOCK input should be selected if the frequency of the input

clock signal is at the target sample rate of the AD9226. The

input clock signal is ac-coupled and level-shifted to the switch-

ing threshold of a 74VHC02 clock driver. The AUXCLK input

should be selected in applications requiring the lowest jitter and

SNR performance (i.e., IF Undersampling characterization). It

allows the user to apply a clock input signal that is 4

×

the target

sample rate of the AD9226. A low-jitter, differential divide-by-4

counter, the MC100EL33D, provides a 1

×

clock output that is

subsequently returned back to the CLOCK input via JP7. For

example, a 260 MHz signal (sinusoid) will be divided down to

a 65 MHz signal for clocking the ADC. Note, R1 must be

removed with the AUXCLK interface. Lower jitter is often

achieved with this interface since many RF signal generators

display improved phase noise at higher output frequencies and

the slew rate of the sinusoidal output signal is 4

×

that of a 1

×

signal of equal amplitude.

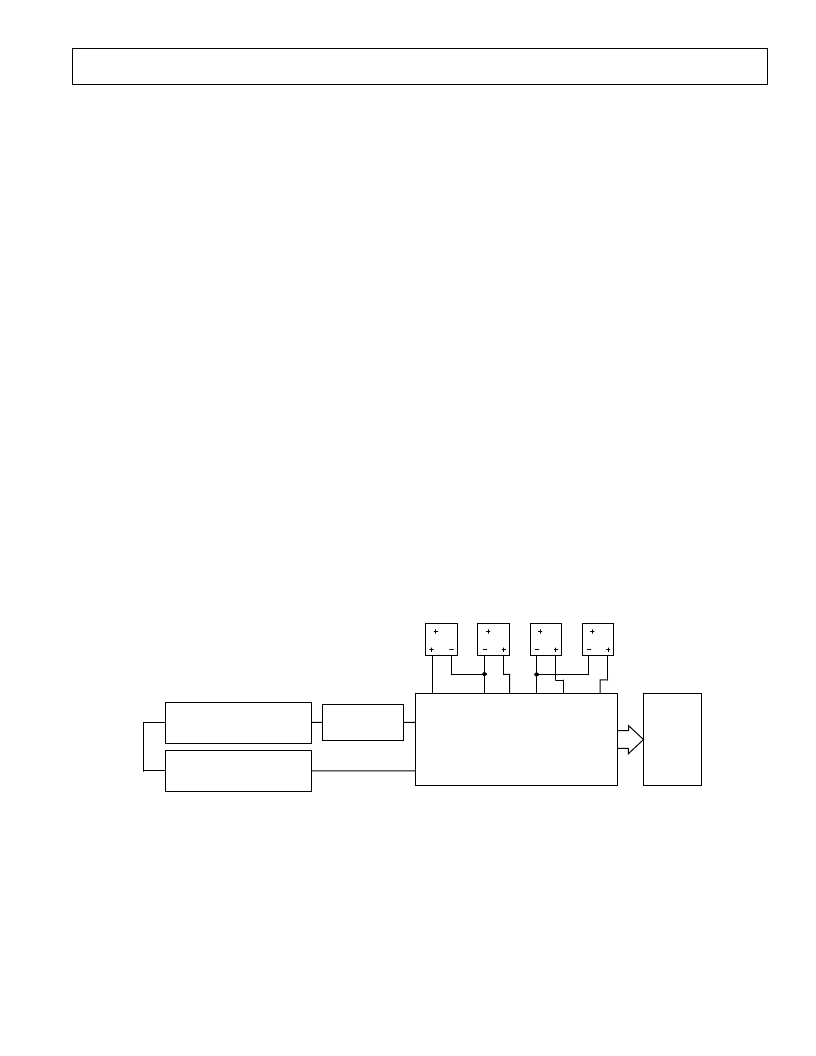

Figure 20 shows the bench characterization setup used to evalu-

ate the AD9226

’

s ac performance for many of the data sheet

characterization curves. Signal and Clock RF generators A and

B are high-frequency,

“

very

”

low-phase noise frequency sources.

These generators should be phase locked by sharing the same

10 MHz REF signal (located on the instruments back panel) to

allow for nonwindowed, coherent FFTs. Also, the AUXCLK

option on the AD9226 evaluation board should be used to

achieve the best SNR performance. Since the distortion and

broadband noise of an RF generator can often be a limiting

factor in measuring the true performance of an ADC, a high Q

passive bandpass filter should be inserted between the generator

and AD9226 evaluation board.

5V

5V

3V

3V

AVDD

GND

GND

DUT

DVDD

DVDD

DUT

AVDD

DSP

EQUIPMENT

S4

INPUT

xFMR

S1

INPUT

CLOCK

AD9226

EVALUATION BOARD

1 MHz

BANDPASS FILTER

SIGNAL SYNTHESIZER

65(OR 260 MHz), 4V p-p

HP8644

OUTPUT

WORD

(P1)

S4

AUX CLOCK

( 4)

REFIN

CLK SYNTHESIZER

65(OR 260 MHz), 4V p-p

HP8644

10 MHz

REFOUT

Figure 20. Evaluation Board Connections

相關PDF資料 |

PDF描述 |

|---|---|

| AD9226-EB | Complete 12-Bit, 65 MSPS ADC Converter |

| AD9226AST | Complete 12-Bit, 65 MSPS ADC Converter |

| AD9226ARS | Complete 12-Bit, 65 MSPS ADC Converter |

| AD9228 | Quad, 12-bit, 40/65 MSPS Serial LVDS 1.8 V A/D Converter |

| AD9228-65EB | Quad, 12-bit, 40/65 MSPS Serial LVDS 1.8 V A/D Converter |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9226_01 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Complete 12-Bit, 65 MSPS ADC Converter |

| AD9226ARS | 功能描述:IC ADC 12BIT 65MSPS 28-SSOP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數:12 采樣率(每秒):3M 數據接口:- 轉換器數目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商設備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數目和類型:- |

| AD9226ARSRL | 功能描述:IC ADC 12BIT 65MSPS 28-SSOP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數:12 采樣率(每秒):3M 數據接口:- 轉換器數目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商設備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數目和類型:- |

| AD9226ARSZ | 功能描述:IC ADC 12BIT 65MSPS 28-SSOP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD9226ARSZRL | 功能描述:IC ADC 12BIT 65MSPS 28SSOP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

發布緊急采購,3分鐘左右您將得到回復。