- 您現在的位置:買賣IC網 > PDF目錄373961 > AD9226AST (ANALOG DEVICES INC) Complete 12-Bit, 65 MSPS ADC Converter PDF資料下載

參數資料

| 型號: | AD9226AST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | Complete 12-Bit, 65 MSPS ADC Converter |

| 中文描述: | 1-CH 12-BIT FLASH METHOD ADC, PARALLEL ACCESS, PQFP48 |

| 封裝: | PLASTIC, LQFP-48 |

| 文件頁數: | 17/28頁 |

| 文件大小: | 1480K |

| 代理商: | AD9226AST |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

REV. 0

AD9226

–17–

The low-impedance VREF output can be used to provide dc

bias levels to the fixed VINB pin and the signal on VINA. Fig-

ure 9b shows the VREF configured for 2.0 V, thus the input

range of the ADC is 1.0 V to 3.0 V. Other input ranges could

be selected by changing VREF.

When the inputs are biased from the reference (Figure 9b),

there may be a slight degeneration of dynamic performance. A

midsupply output level is available at the

CM

LEVEL pin of the

LQFP package.

10 F

VINA

VINB

AD9226

V

IN

VREF

15pF

0.1 F

10 F

0.1 F

0.1 F

R

0.1 F

10 F

R

S

R

S

C1

10 F

CAPB

CAPT

R

R

+5V

–

5V

C2

0.1 F

R

0.1 F

V

V

+1V

0V

–

1V

3.5

2.5

1.5

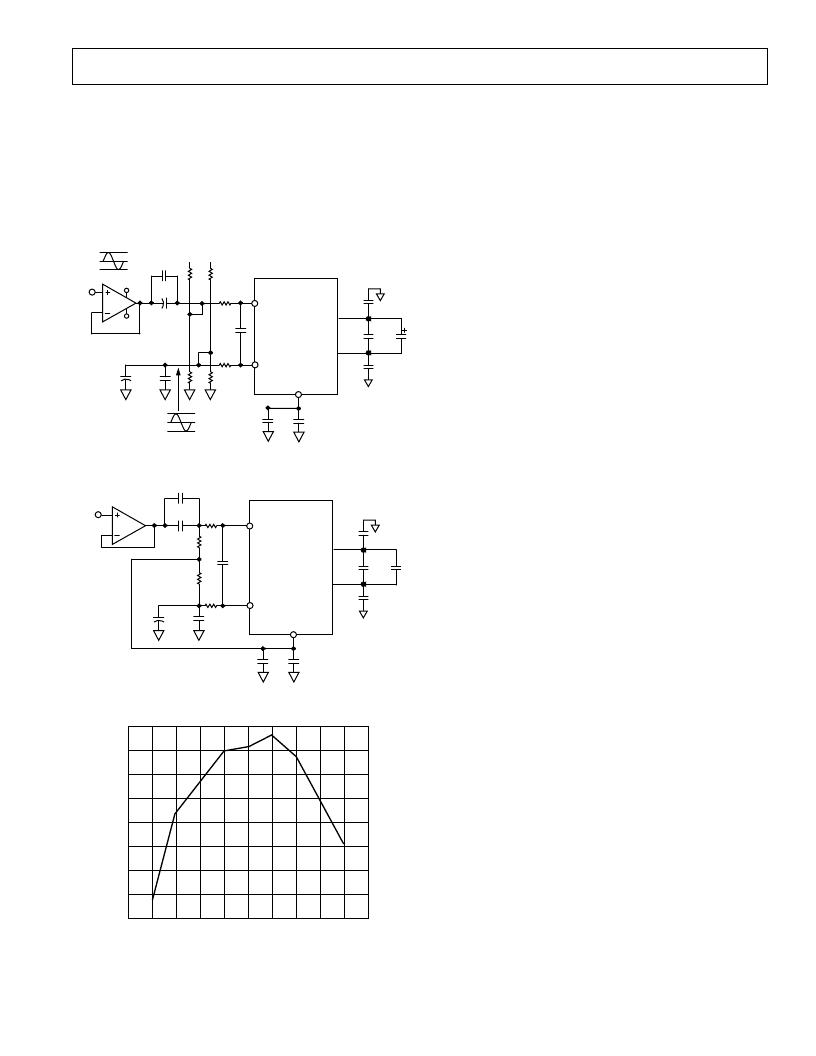

Figure 9a. AC-Coupled Input Configuration

10 F

VINA

VINB

AD9226

V

IN

VREF

15pF

0.1 F

10 F

0.1 F

0.1 F

1k

1k

0.1 F

10 F

0.1 F

R

S

R

S

10 F

0.1 F

CAPB

CAPT

Figure 9b. Alternate AC-Coupled Input Configuration

0

–

84

–

83

–

82

–

81

–

80

–

79

–

78

–

77

–

76

0.5

1.0

1.5

2.0

2.5

volts

3.0

3.5

4.0

4.5

5.0

d

Figure 10. THD vs. Common-Mode Voltage

(2 V Differential Input Span, f

IN

= 10 MHz)

Figure 10 illustrates the relation between common-mode voltage

and THD. Note that optimal performance occurs when the

reference voltage is set to 2.0 V (input span = 2.0 V).

DC-COUPLING AND INTERFACE ISSUES

Many applications require the analog input signal to be dc-coupled

to the AD9226. An operational amplifier can be configured to

rescale and level-shift the input signal to make it compatible

with the selected input range of the ADC.

The selected input range of the AD9226 should be considered

with the headroom requirements of the particular op amp to

prevent clipping of the signal. Many of the new high-performance

op amps are specified for only

±

5 V operation and have limited

input/output swing capabilities. Also, since the output of a dual

supply amplifier can swing below absolute minimum (

–

0.3 V),

clamping its output should be considered in some applications

(see Figure 8). When single-ended, dc-coupling is needed, the

use of the AD8138 in a differential configuration (Figure 9a) is

highly recommended.

Simple Op Amp Buffer

In the simplest case, the input signal to the AD9226 will already

be biased at levels in accordance with the selected input range. It

is necessary to provide an adequately low source impedance for

the VINA and VINB analog pins of the ADC.

REFERENCE OPERATION

The AD9226 contains an on-board bandgap reference that

provides a pin-strappable option to generate either a 1 V or

2 V output. With the addition of two external resistors, the user

can generate reference voltages between 1 V and 2 V. See

Figures 5a-5f for a summary of the pin-strapping options for the

AD9226 reference configurations. Another alternative is to use

an external reference for designs requiring enhanced accuracy

and/or drift performance described later in this section.

Figure 11a shows a simplified model of the internal voltage refer-

ence of the AD9226. A reference amplifier buffers a 1 V fixed

reference. The output from the reference amplifier, A1, appears

on the VREF pin. The voltage on the VREF pin determines

the full-scale input span of the ADC. This input span equals,

Full-Scale

Input Span

=

VREF

The voltage appearing at the VREF pin, and the state of the

internal reference amplifier, A1, are determined by the voltage

appearing at the SENSE pin. The logic circuitry contains com-

parators that monitor the voltage at the SENSE pin. If the

SENSE pin is tied to AVSS, the switch is connected to the

internal resistor network thus providing a VREF of 2.0 V. If the

SENSE pin is tied to the VREF pin via a short or resistor, the

switch will connect to the SENSE pin. This connection will pro-

vide a VREF of 1.0 V. An external resistor network will provide

an alternative VREF between 1.0 V and 2.0 V (see Figure 12).

Another comparator controls internal circuitry that will disable

the reference amplifier if the SENSE pin is tied to AVDD.

Disabling the reference amplifier allows the VREF pin to be

driven by an external voltage reference.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9226ARS | Complete 12-Bit, 65 MSPS ADC Converter |

| AD9228 | Quad, 12-bit, 40/65 MSPS Serial LVDS 1.8 V A/D Converter |

| AD9228-65EB | Quad, 12-bit, 40/65 MSPS Serial LVDS 1.8 V A/D Converter |

| AD9229BCP-50 | Quad 12-Bit, 50/65 MSPS Serial LVDS 3V A/D Converter |

| AD9229BCP-65 | Quad 12-Bit, 50/65 MSPS Serial LVDS 3V A/D Converter |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9226ASTRL | 功能描述:IC ADC 12BIT 65MSPS 48-LQFP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數:12 采樣率(每秒):3M 數據接口:- 轉換器數目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商設備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數目和類型:- |

| AD9226ASTZ | 功能描述:IC ADC 12BIT 65MSPS 48-LQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:microPOWER™ 位數:8 采樣率(每秒):1M 數據接口:串行,SPI? 轉換器數目:1 功率耗散(最大):- 電壓電源:模擬和數字 工作溫度:-40°C ~ 125°C 安裝類型:表面貼裝 封裝/外殼:24-VFQFN 裸露焊盤 供應商設備封裝:24-VQFN 裸露焊盤(4x4) 包裝:Digi-Reel® 輸入數目和類型:8 個單端,單極 產品目錄頁面:892 (CN2011-ZH PDF) 其它名稱:296-25851-6 |

| AD9226ASTZRL | 功能描述:IC ADC 12BIT 65MSPS 48LQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD9226-EB | 制造商:Analog Devices 功能描述:EVAL BD FOR AD9226 ADC CNVRTR - Bulk |

| AD9226-LQFP-EB | 制造商:AD 制造商全稱:Analog Devices 功能描述:Complete 12-Bit, 65 MSPS ADC Converter |

發布緊急采購,3分鐘左右您將得到回復。