- 您現在的位置:買賣IC網 > PDF目錄373963 > AD9445BSVZ-125 (ANALOG DEVICES INC) 14-Bit, 105/125 MSPS, IF Sampling ADC PDF資料下載

參數資料

| 型號: | AD9445BSVZ-125 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 14-Bit, 105/125 MSPS, IF Sampling ADC |

| 中文描述: | 1-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| 封裝: | LEAD FREE, PLASTIC, MS-026-AED, TQFP-100 |

| 文件頁數: | 28/40頁 |

| 文件大小: | 965K |

| 代理商: | AD9445BSVZ-125 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

AD9445

OPERATIONAL MODE SELECTION

Data Format Select

The data format select (DFS) pin of the AD9445 determines

the coding format of the output data. This pin is 3.3 V CMOS-

compatible, with logic high (or AVDD1, 3.3 V) selecting twos

complement and DFS logic low (AGND) selecting offset binary

format. Table 10 summarizes the output coding.

Rev. 0 | Page 28 of 40

Output Mode Select

The OUPUT MODE pin controls the logic compatibility, as well

as the pinout of the digital outputs. This pin is a CMOS-compatible

input. With OUTPUT MODE = 0 (AGND), the AD9445 outputs

are CMOS compatible, and the pin assignment for the device is

as defined in Table 8. With OUTPUT MODE = 1 (AVDD1, 3.3

V), the AD9445 outputs are LVDS compatible, and the pin

assignment for the device is as defined in Table 7.

Duty Cycle Stabilizer

The DCS circuit is controlled by the DCS MODE pin; a CMOS

logic low (AGND) on DCS MODE enables the DCS, and logic

high (AVDD1, 3.3 V) disables the controller.

RF ENABLE

The RF ENABLE pin is a CMOS-compatible control pin that

optimizes the configuration of the AD9445 analog front end.

The crossover analog input frequency for determining the

RF ENABLE connection differs for the 105 MSPS and 125 MSPS

speed grades. For the 125 MSPS speed grade, connecting the

RF ENABLE to AGND optimizes SFDR performance for appli-

cations with analog input frequencies <210 MHz. For applications

with analog inputs >210 MHz, this pin should be connected to

AVDD1 for optimum SFDR performance. Connecting this pin to

AVDD1 reconfigures the ADC, thereby improving high IF and RF

spurious performance. Operating in this mode increases power dis-

sipation from AVDD2 by 150 mW to 200 mW For the 105 MSPS

speed grade, connecting RF ENABLE to AGND optimizes SFDR

performance for applications with analog input frequencies

<230 MHz. For applications with analog inputs >230 MHz, this

pin should be connected to AVDD1 to optimize performance.

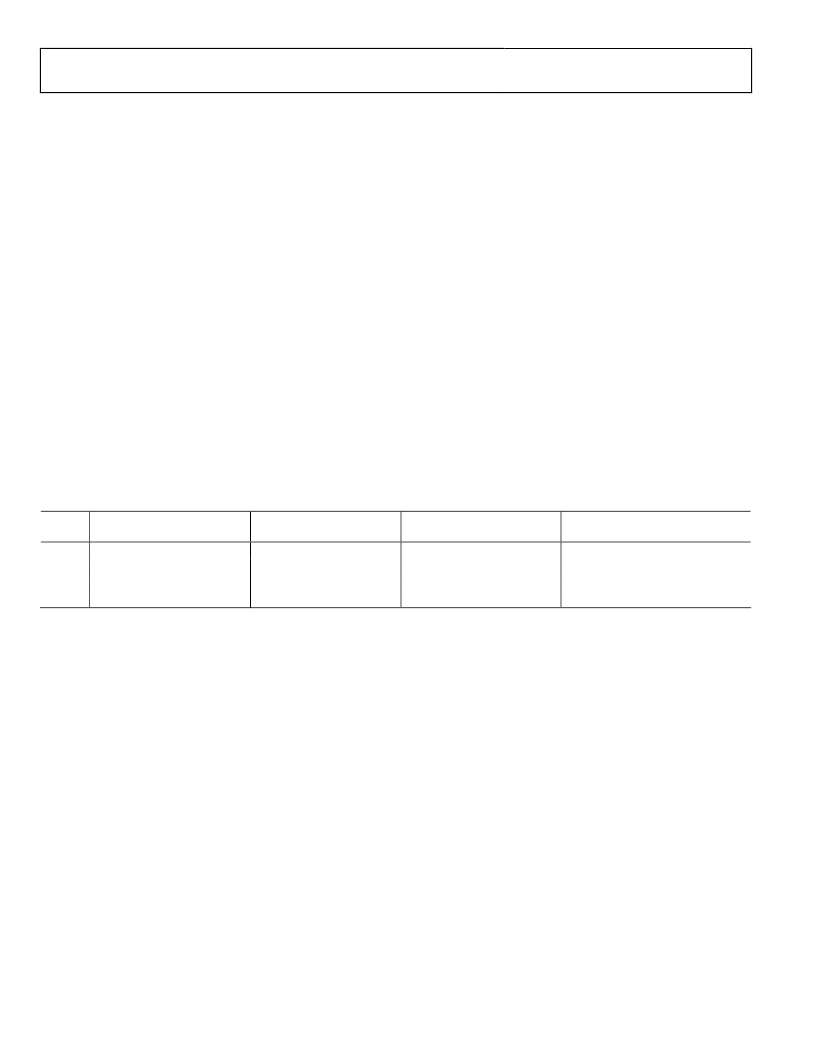

Table 10. Digital Output Coding

VIN+ VIN

Input Span = 3.2 V p-p (V)

16,383 +1.600

8192

0

8191

0.000195

0

1.60

Code

VIN+ VIN

Input Span = 2 V p-p (V)

+1.000

0

0.000122

1.00

Digital Output

Offset Binary (D13D0)

11 1111 1111 1111

10 0000 0000 0000

01 1111 1111 1111

00 0000 0000 0000

Digital Output

Twos Complement (D13D0)

01 1111 1111 1111

00 0000 0000 0000

11 1111 1111 1111

10 0000 0000 0000

相關PDF資料 |

PDF描述 |

|---|---|

| AD9445 | 14-Bit, 105/125 MSPS, IF Sampling ADC |

| AD9445-BB-LVDS | 14-Bit, 105/125 MSPS, IF Sampling ADC |

| AD9445-BB-PCB | 14-Bit, 105/125 MSPS, IF Sampling ADC |

| AD9445-IF-LVDS | 14-Bit, 105/125 MSPS, IF Sampling ADC |

| AD9446BSVZ-100 | 16-Bit, 80/100 MSPS ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9445-IF-LVDS | 制造商:AD 制造商全稱:Analog Devices 功能描述:14-Bit, 105/125 MSPS, IF Sampling ADC |

| AD9445-IF-LVDS/PCB | 制造商:Analog Devices 功能描述:Evaluation Kit For 14-Bit, 105/125 MAPA, IF Sampling ADC 制造商:Analog Devices 功能描述:EVAL KIT FOR 14BIT, 105/125 MSPS, IF SAMPLING ADC - Bulk |

| AD9445IF-LVDS/PCBZ | 制造商:Analog Devices 功能描述:Evaluation Board For AD9445IF 制造商:Analog Devices 功能描述:14-BIT 125 MSPS ADC IF EVAL BD - Bulk |

| AD9445-IF-LVDSPCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:High Speed ADC USB FIFO Evaluation Kit |

| AD9445-IF-PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:14-Bit, 105/125 MSPS, IF Sampling ADC |

發布緊急采購,3分鐘左右您將得到回復。