- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9845A (Analog Devices, Inc.) Complete 12-Bit 30 MSPS CCD Signal Processor PDF資料下載

參數資料

| 型號: | AD9845A |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Complete 12-Bit 30 MSPS CCD Signal Processor |

| 中文描述: | 完整的12位30 MSPS的CCD信號處理器 |

| 文件頁數: | 7/22頁 |

| 文件大小: | 252K |

| 代理商: | AD9845A |

REV. 0

AD9845A

–7–

DEFINITIONS OF SPECIFICATIONS

DIFFERENTIAL NONLINEARITY (DNL)

An ideal ADC exhibits code transitions that are exactly 1 LSB

apart. DNL is the deviation from this ideal value. Thus every code

must have a finite width. No missing codes guaranteed to 12-bit

resolution indicates that all 4096 codes, respectively, must be

present over all operating conditions.

PEAK NONLINEARITY

Peak nonlinearity, a full signal chain specification, refers to the

peak deviation of the output of the AD984x from a true straight

line. The point used as “zero scale” occurs 1/2 LSB before the

first code transition. “Positive full scale” is defined as a Level 1,

1/2 LSB beyond the last code transition. The deviation is measured

from the middle of each particular output code to the true straight

line. The error is then expressed as a percentage of the 2 V ADC

full-scale signal. The input signal is always appropriately gained up

to fill the ADC’s full-scale range.

TOTAL OUTPUT NOISE

The rms output noise is measured using histogram techniques.

The standard deviation of the ADC output codes is calculated

in LSB, and represents the rms noise level of the total signal

chain at the specified gain setting. The output noise can be

converted to an equivalent voltage, using the relationship 1 LSB

= (ADC Full Scale/2

N

codes) when N is the bit resolution of the

ADC. For the AD9845A, 1 LSB is 500 μV.

POWER SUPPLY REJECTION (PSR)

The PSR is measured with a step change applied to the supply

pins. This represents a very high frequency disturbance on the

AD984x’s power supply. The PSR specification is calculated

from the change in the data outputs for a given step change in

the supply voltage.

INTERNAL DELAY FOR SHP/SHD

The internal delay (also called aperture delay) is the time delay

that occurs from when a sampling edge is applied to the AD984x

until the actual sample of the input signal is held. Both SHP and

SHD sample the input signal during the transition from low to

high, so the internal delay is measured from each clock’s rising

edge to the instant the actual internal sample is taken.

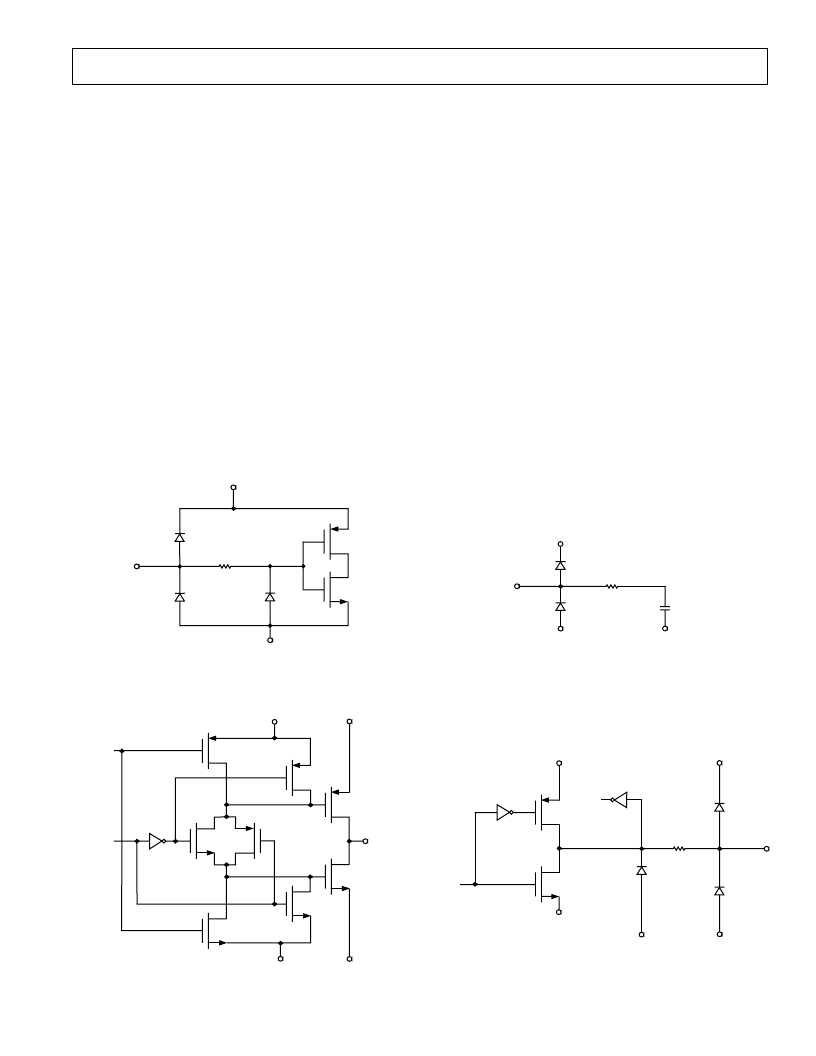

EQUIVALENT INPUT CIRCUITS

330

DVDD

DVSS

Figure 1. Digital Inputs—SHP, SHD, DATACLK, CLPOB,

CLPDM, HD, VD, PBLK, SCK, SL

DVDD

DVSS

DRVSS

DRVDD

THREE-

STATE

DATA

DOUT

Figure 2. Data Outputs—D0–D11

60

ACVDD

ACVSS

ACVSS

Figure 3. CCDIN (Pin 30)

330

DVDD

DVSS

DVDD

DVSS

DVSS

DATA IN

RNW

DATA OUT

Figure 4. SDATA (Pin 47)

相關PDF資料 |

PDF描述 |

|---|---|

| AD9845AJST | Complete 12-Bit 30 MSPS CCD Signal Processor |

| AD9846A | Complete 10-Bit 30 MSPS CCD Signal Processor |

| AD9846AJST | Complete 10-Bit 30 MSPS CCD Signal Processor |

| AD9847 | 10-Bit 40 MSPS CCD Signal Processor with Integrated Timing Driver |

| AD9847AKST | 10-Bit 40 MSPS CCD Signal Processor with Integrated Timing Driver |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9845AJST | 制造商:Analog Devices 功能描述:CCD Signal Processor 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:12 BIT 30 MHZ AFE NO PXGA - Bulk |

| AD9845AJSTRL | 制造商:Analog Devices 功能描述:CCD Signal Processor 48-Pin LQFP T/R 制造商:Analog Devices 功能描述:CCD SGNL PROCESSOR 48LQFP - Tape and Reel |

| AD9845B | 制造商:AD 制造商全稱:Analog Devices 功能描述:Complete 12-Bit 30 MSPS CCD Signal Processor |

| AD9845BJST | 制造商:Analog Devices 功能描述:CCD SGNL PROCESSOR 48LQFP - Trays 制造商:Rochester Electronics LLC 功能描述: |

| AD9845BJSTRL | 制造商:Analog Devices 功能描述:CCD SGNL PROCESSOR 48LQFP - Tape and Reel 制造商:Rochester Electronics LLC 功能描述:12 BIT 30MHZ AFE NO PXGA - Tape and Reel |

發布緊急采購,3分鐘左右您將得到回復。