- 您現在的位置:買賣IC網 > PDF目錄373970 > AD9876BST (ANALOG DEVICES INC) Broadband Modem Mixed-Signal Front End PDF資料下載

參數資料

| 型號: | AD9876BST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網絡 |

| 英文描述: | Broadband Modem Mixed-Signal Front End |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP48 |

| 封裝: | LQFP-48 |

| 文件頁數: | 4/24頁 |

| 文件大小: | 666K |

| 代理商: | AD9876BST |

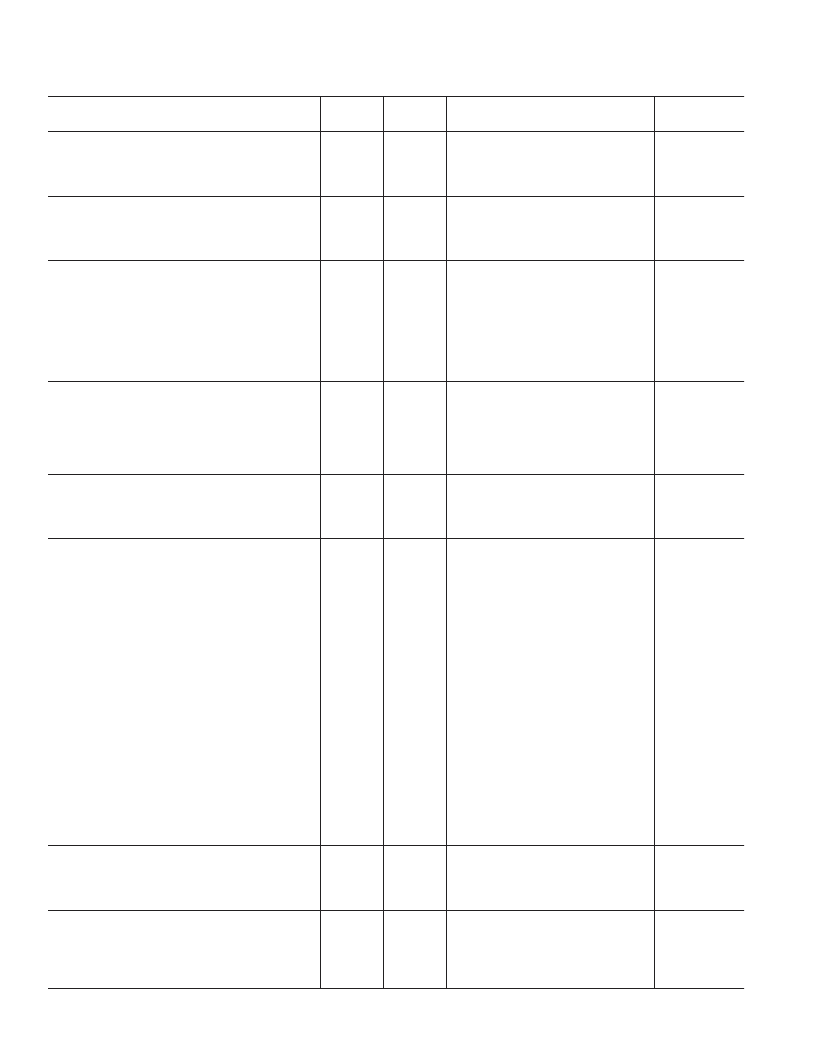

REV. A

AD9876

–4–

Test

Level

Parameter

Temp

Min

Typ

Max

Unit

Tx PATH INTERFACE

Maximum Input Nibble Rate, 2

×

Interpolation

Tx Setup Time (t

SU

)

Tx Hold Time (t

HD

)

Rx PATH INTERFACE

Maximum Output Nibble Rate

Rx Data Valid Time (t

VT

)

Rx Data Hold Time (t

HT

)

SERIAL CONTROL BUS

Maximum SCLK Frequency (f

SCLK

)

Clock Pulsewidth High (t

PWH

)

Clock Pulsewidth Low (t

PWL

)

Clock Rise/Fall Time

Data/Chip-Select Setup Time (t

DS

)

Data Hold Time (t

DH

)

Data Valid Time (t

DV

)

CMOS LOGIC INPUTS

Logic “1” Voltage

Logic “0” Voltage

Logic “1” Current

Logic “0” Current

Input Capacitance

Full

Full

Full

II

II

II

128

3.0

0

MHz

ns

ns

Full

Full

Full

II

II

II

110

MHz

ns

ns

3.0

1.5

Full

Full

Full

Full

Full

Full

Full

II

II

II

II

II

II

II

25

18

18

MHz

ns

ns

ms

ns

ns

ns

1

25

0

20

Full

Full

Full

Full

25

°

C

II

II

II

II

III

V

DRVDD

– 0.7

V

V

μ

A

μ

A

μ

F

0.4

12

12

3

CMOS LOGIC OUTPUTS (1 mA Load)

Logic “1” Voltage

Logic “0” Voltage

Digital Output Rise/Fall Time

Full

Full

Full

II

II

II

V

DRVDD

– 0.6

V

V

ns

0.4

2.5

1.5

POWER SUPPLY

All Blocks Powered Up

I

S_TOTAL

(Total Supply Current)

I

S_TOTAL

(

Tx QUIET

Pin Asserted)

Digital Supply Current (I

DRVDD

+ I

DVDD

)

Analog Supply Current (I

AVDD

)

Power Consumption of Functional Blocks:

Rx LPF

ADC and SPGA

Rx Reference

Interpolator

DAC

PLL-B

PLL-A

Voltage Regulator Controller

All Blocks Powered Down

Supply Current I

S

, f

OSCIN

= 32 MHz

Supply Current I

S

, f

OSCIN

Idle

Power Supply Rejection

Tx Path (

V

S

= 10%)

Rx Path (

V

S

= 10%)

RECEIVE-TO-TRANSMIT ISOLATION

(10 MHz, Full-Scale Sine Wave Output/Output)

Isolation: Tx Path to Rx Path, Gain = +36 dB

Isolation: Rx Path to Tx Path, Gain = –6 dB

Full

25

°

C

25

°

C

25

°

C

I

III

III

III

262

172

77

185

288

mA

mA

mA

mA

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

25

°

C

III

III

III

III

III

III

III

III

110

55

2

33

18

8

24

1

mA

mA

mA

mA

mA

mA

mA

mA

Full

Full

II

II

19

10

22

12

mA

mA

25

°

C

25

°

C

III

III

62

54

dB

dB

25

°

C

25

°

C

III

III

–75

–70

dB

dB

VOLTAGE REGULATOR CONTROLLER

Output Voltage (V

FB

with SI2301 Connected)

Line Regulation (

V

FB%

/

V

DVDD%

×

100%)

Load Regulation (

V

FB

/

I

LOAD

)

Maximum Load Current (I

LOAD

)

Full

25

°

C

25

°

C

Full

I

III

III

II

1.25

1.30

100

60

1.35

V

%

m

mA

250

Specifications subject to change without notice.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9876BSTRL | Broadband Modem Mixed-Signal Front End |

| AD9877 | Mixed-Signal Front End Set-Top Box, Cable Modem |

| AD9877ABS | Mixed-Signal Front End Set-Top Box, Cable Modem |

| AD9877-EB | Mixed-Signal Front End Set-Top Box, Cable Modem |

| AD9882KST-100 | Dual Interface for Flat Panel Displays |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9876BSTRL | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| AD9876EB | 制造商:Analog Devices 功能描述: |

| AD9876-EB | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

| AD9877 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Mixed-Signal Front End Set-Top Box, Cable Modem |

| AD9877ABS | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。