- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373983 > ADF4252BCP-REEL7 (ANALOG DEVICES INC) Dual Fractional-N/Integer-N Frequency Synthesizer PDF資料下載

參數(shù)資料

| 型號: | ADF4252BCP-REEL7 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | XO, clock |

| 英文描述: | Dual Fractional-N/Integer-N Frequency Synthesizer |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 3000 MHz, QCC24 |

| 封裝: | MO-220-VGGD, LFCSP-24 |

| 文件頁數(shù): | 11/28頁 |

| 文件大小: | 384K |

| 代理商: | ADF4252BCP-REEL7 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

REV. B

ADF4252

–11–

CIRCUIT DESCRIPTION

Reference Input Section

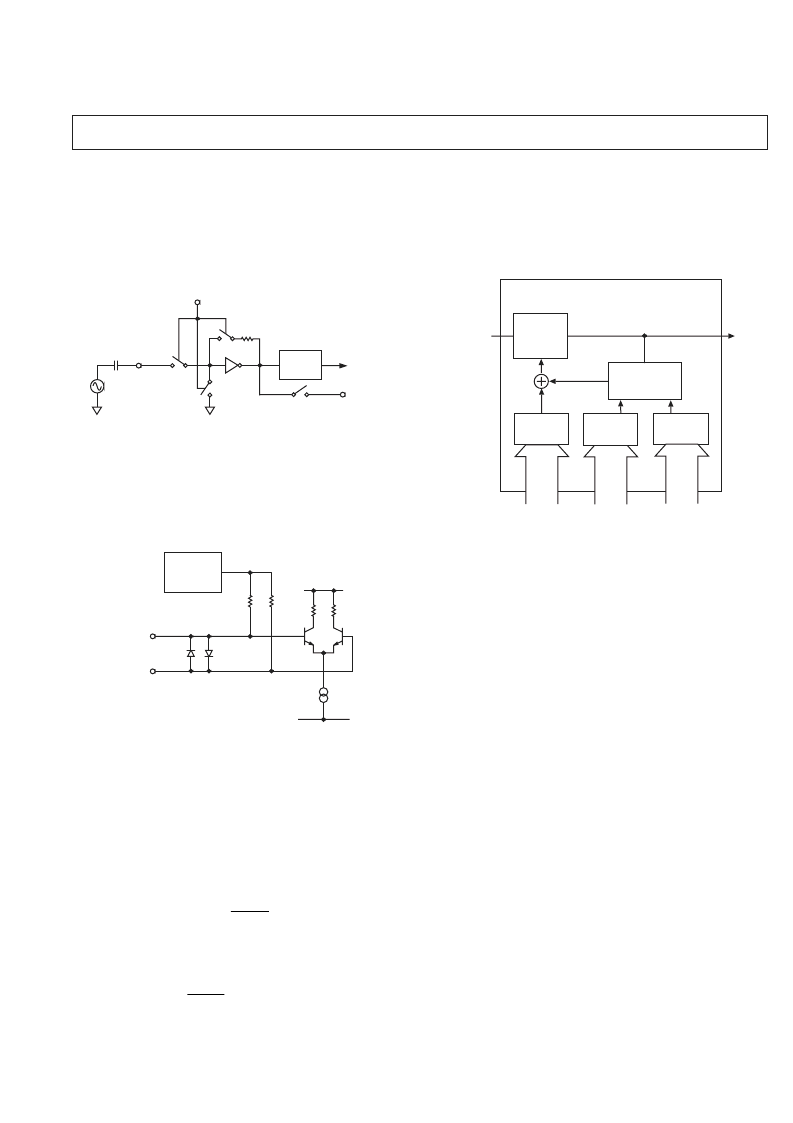

The reference input stage is shown in Figure 3. SW1 and SW2

are normally closed switches. SW3 is normally open. When

power-down is initiated, SW3 is closed and SW1 and SW2 are

opened. This ensures that there is no loading of the REF

IN

pin

on power-down.

POWER-DOWN

CONTROL

REF

IN

NC

NC

NO

SW3

SW2

SW1

100k

BUFFER

TO R

COUNTER

NC = NORMALLY CLOSED

NO = NORMALLY OPEN

REF

OUT

XOEB

Figure 3. Reference Input Stage

RF and IF Input Stage

The RF input stage is shown in Figure 4. The IF input stage is

the same. It is followed by a two-stage limiting amplifier to

generate the CML clock levels needed for the N counter.

2k

2k

1.6V

BIAS

GENERATOR

RF

IN

A

RF

IN

B

V

DD

1

A

GND

Figure 4. RF Input Stage

RF INT Divider

The RF INT CMOS counter allows a division ratio in the PLL

feedback counter. Division ratios from 31 to 255 are allowed.

INT, FRAC, MOD, and R Relationship

The INT, FRAC, and MOD values, in conjunction with the

RF R counter, make it possible to generate output frequencies

that are spaced by fractions of the RF phase frequency detector

(PFD). The equation for the RF VCO frequency (

RF

OUT

) is

RF

F

INT

FRAC

MOD

OUT

PFD

=

×

+

(1)

where

RF

OUT

is the output frequency of external voltage controlled

oscillator (VCO).

(

1

F

REF

D

R

PFD

IN

=

×

+

)

(2)

REF

IN

= the reference input frequency,

D

= RF REF

IN

doubler

bit,

R

= the preset divide ratio of the binary 4-bit program-

mable reference counter (1 to 15),

INT

= the preset divide ratio of

the binary 8-bit counter (31 to 255),

MOD

= the preset modulus

ratio of binary 12-bit programmable FRAC counter (2 to 4095),

and

FRAC

= the preset fractional ratio of the binary 12-bit

programmable FRAC counter (0 to MOD).

N = INT + FRAC/MOD

FROM RF

INPUT STAGE

TO PFD

RF N DIVIDER

THIRD ORDER

FRACTIONAL

INTERPOLATOR

MOD

REG

INT

REG

FRAC

VALUE

N-COUNTER

Figure 5. N Counter

RF R Counter

The 4-bit RF R counter allows the input reference frequency

(REF

IN

) to be divided down to produce the reference clock to

the RF PFD. Division ratios from 1 to 15 are allowed.

IF R Counter

The 15-bit IF R counter allows the input reference frequency

(REF

IN

) to be divided down to produce the reference clock to

the IF PFD. Division ratios from 1 to 32767 are allowed.

IF Prescaler (P/P + 1)

The dual modulus IF prescaler (P/P + 1), along with the IF A

and B counters, enables the large division ratio, N, to be realized

(N = PB + A). Operating at CML levels, it takes the clock from

the IF input stage and divides it down to a manageable frequency

for the CMOS IF A and B counters.

IF A and B Counters

The IF A and B CMOS counters combine with the dual modulus

IF prescaler to allow a wide ranging division ratio in the PLL

feedback counter. The counters are guaranteed to work when the

prescaler output is 150 MHz or less.

Pulse Swallow Function

The IF A and B counters, in conjunction with the dual modulus

IF prescaler, make it possible to generate output frequencies

that are spaced only by the reference frequency divided by R.

See Device Programming after Initial Power-Up section for

examples. The equation for the IF VCO (

IF

OUT

) frequency is

(

IF

P

B

A

F

OUT

PFD

=

×

)

+

[

]

×

(3)

where

IF

OUT

= the output frequency of the external voltage controlled

oscillator (VCO),

P

= the preset modulus of IF dual modulus

prescaler,

B

= the preset divide ratio of the binary 12-bit counter

(3 to 4095), and

A

= the preset divide ratio of the binary 6-bit

swallow counter (0 to 63).

F

PFD

is obtained using Equation 2.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADF4360-3BCP | Integrated Synthesizer and VCO |

| ADF4360-4BCP | Integrated Synthesizer and VCO |

| ADF4360-1BCP | Integrated Synthesizer and VCO |

| ADF4360-2 | Integrated Synthesizer and VCO |

| ADF4360-2BCP | Integrated Synthesizer and VCO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADF4252BCPZ | 功能描述:IC PLL FREQ SYNTHESIZER 24-LFCSP RoHS:是 類別:集成電路 (IC) >> 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘發(fā)生器,PLL,頻率合成器 系列:- 標(biāo)準(zhǔn)包裝:2,000 系列:- 類型:PLL 頻率合成器 PLL:是 輸入:晶體 輸出:時(shí)鐘 電路數(shù):1 比率 - 輸入:輸出:1:1 差分 - 輸入:輸出:無/無 頻率 - 最大:1GHz 除法器/乘法器:是/無 電源電壓:4.5 V ~ 5.5 V 工作溫度:-20°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-LSSOP(0.175",4.40mm 寬) 供應(yīng)商設(shè)備封裝:16-SSOP 包裝:帶卷 (TR) 其它名稱:NJW1504V-TE1-NDNJW1504V-TE1TR |

| ADF4252BCPZ-R7 | 功能描述:IC PLL FREQ SYNTHESIZER 24LFCSP RoHS:是 類別:集成電路 (IC) >> 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘發(fā)生器,PLL,頻率合成器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:Precision Edge® 類型:時(shí)鐘/頻率合成器 PLL:無 輸入:CML,PECL 輸出:CML 電路數(shù):1 比率 - 輸入:輸出:2:1 差分 - 輸入:輸出:是/是 頻率 - 最大:10.7GHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-VFQFN 裸露焊盤,16-MLF? 供應(yīng)商設(shè)備封裝:16-MLF?(3x3) 包裝:帶卷 (TR) 其它名稱:SY58052UMGTRSY58052UMGTR-ND |

| ADF4252BCPZ-RL | 功能描述:IC PLL FREQ SYNTHESIZER 24LFCSP RoHS:是 類別:集成電路 (IC) >> 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘發(fā)生器,PLL,頻率合成器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:Precision Edge® 類型:時(shí)鐘/頻率合成器 PLL:無 輸入:CML,PECL 輸出:CML 電路數(shù):1 比率 - 輸入:輸出:2:1 差分 - 輸入:輸出:是/是 頻率 - 最大:10.7GHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-VFQFN 裸露焊盤,16-MLF? 供應(yīng)商設(shè)備封裝:16-MLF?(3x3) 包裝:帶卷 (TR) 其它名稱:SY58052UMGTRSY58052UMGTR-ND |

| ADF4350 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Wideband Synthesizer with Integrated VCO |

| ADF4350ABCPZ | 制造商:Analog Devices 功能描述:F-N WITH HIGH PERFORMANCE INTEGRATED VCO - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。