- 您現在的位置:買賣IC網 > PDF目錄374032 > ADSP-21060L (Analog Devices, Inc.) ADSP-2106x SHARC DSP Microcomputer Family PDF資料下載

參數資料

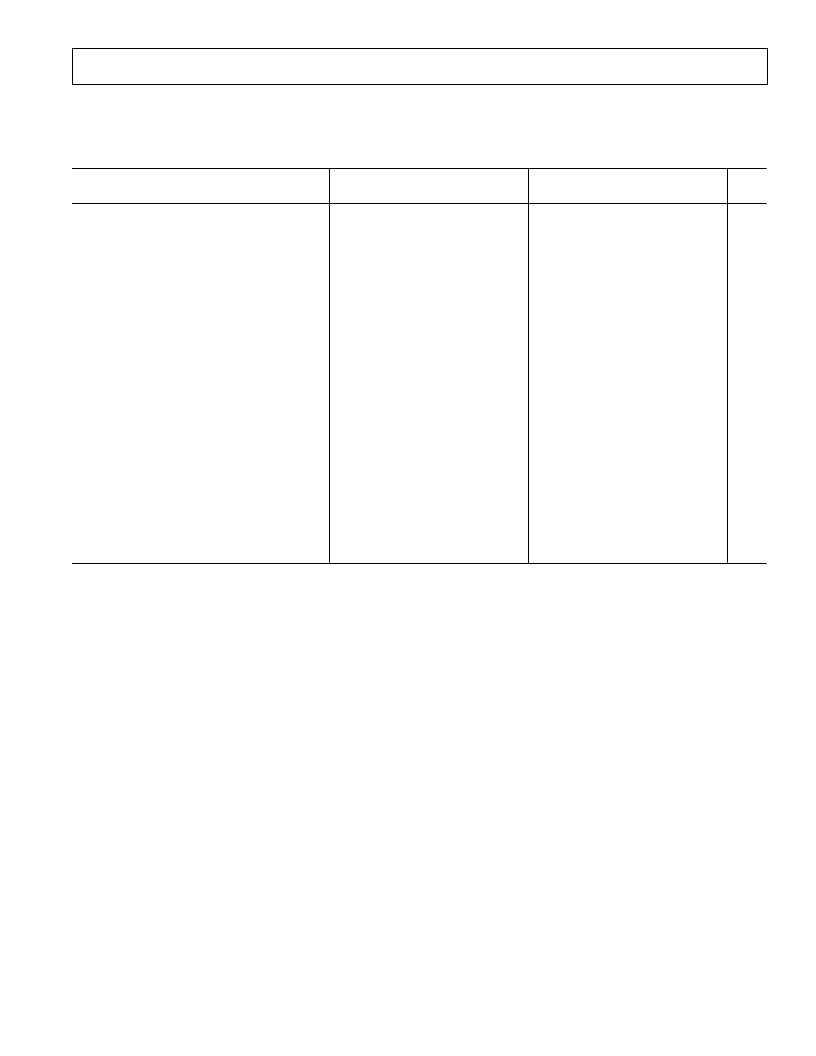

| 型號: | ADSP-21060L |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | ADSP-2106x SHARC DSP Microcomputer Family |

| 中文描述: | 的ADSP - 2106x SHARC處理器DSP的微機家庭 |

| 文件頁數: | 25/47頁 |

| 文件大小: | 366K |

| 代理商: | ADSP-21060L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

ADSP-21060/ADSP-21060L

–25–

REV. D

ADSP-21060

Min

ADSP-21060L

Min

Parameter

Max

Max

Units

Timing Requirements:

t

HBGRCSV

HBG

Low to

RD

/

WR

/

CS

Valid

1

t

SHBRI

HBR

Setup before CLKIN

2

t

HHBRI

HBR

Hold before CLKIN

2

t

SHBGI

HBG

Setup before CLKIN

t

HHBGI

HBG

Hold before CLKIN High

t

SBRI

BR

x,

CPA

Setup before CLKIN

3

t

HBRI

BR

x,

CPA

Hold before CLKIN High

t

SRPBAI

RPBA Setup before CLKIN

t

HRPBAI

RPBA Hold before CLKIN

20+ 5DT/4

20+ 5DT/4

ns

ns

ns

ns

ns

ns

ns

ns

ns

20 + 3DT/4

20 + 3DT/4

14 + 3DT/4

14 + 3DT/4

13 + DT/2

13 + DT/2

6 + DT/2

6 + DT/2

13 + DT/2

13 + DT/2

6 + DT/2

6 + DT/2

21 + 3DT/4

21 + 3DT/4

12 + 3DT/4

12 + 3DT/4

Switching Characteristics:

t

DHBGO

HBG

Delay after CLKIN

t

HHBGO

HBG

Hold after CLKIN

t

DBRO

BR

x Delay after CLKIN

t

HBRO

BR

x Hold after CLKIN

t

DCPAO

CPA

Low Delay after CLKIN

t

TRCPA

CPA

Disable after CLKIN

t

DRDYCS

REDY (O/D) or (A/D) Low from

CS

and

HBR

Low

4

t

TRDYHG

REDY (O/D) Disable or REDY (A/D)

High from

HBG

4

t

ARDYTR

REDY (A/D) Disable from

CS

or

HBR

High

4

7 – DT/8

7 – DT/8

ns

ns

ns

ns

ns

ns

–2 – DT/8

–2 – DT/8

7 – DT/8

7 – DT/8

–2 – DT/8

–2 – DT/8

8 – DT/8

4.5 – DT/8

8 – DT/8

4.5 – DT/8

–2 – DT/8

–2 – DT/8

8.5

9.25

ns

44 + 23DT/16

44 + 23DT/16

ns

10

10

ns

NOTES

1

For first asynchronous access after

HBR

and

CS

asserted, ADDR

31-0

must be a non-MMS value 1/2 t

CK

before

RD

or

WR

goes low or by t

HBGRCSV

after

HBG

goes

low. This is easily accomplished by driving an upper address signal high when

HBG

is asserted. See the “Host Processor Control of the ADSP-2106x” section in the

ADSP-2106x SHARC User’s Manual, Second Edition

.

2

Only required for recognition in the current cycle.

3

CPA

assertion must meet the setup to CLKIN; deassertion does not need to meet the setup to CLKIN.

4

(O/D) = open drain, (A/D) = active drive.

Multiprocessor Bus Request and Host Bus Request

Use these specifications for passing of bus mastership between

multiprocessing ADSP-2106xs (

BR

x) or a host processor

(

HBR

,

HBG

).

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21060LAB-160 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21060KS-133 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21060KS-160 | ADSP-2106x SHARC DSP Microcomputer Family |

| ADSP-21060LKB-160 | RES, 2.2 K SM CHIP 5% 50V 1/16 WATT, 0603 |

| ADSP-21060LKS-133 | ADSP-2106x SHARC DSP Microcomputer Family |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-21060LAB-160 | 功能描述:IC DSP CONTROLLER 32BIT 225BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21060LABZ-160 | 功能描述:IC DSP CONTROLLER 32BIT 225-BGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21060LC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ADSP-21060C/ADSP-21060LC: Industrial Sharc?DSP Microcomputer Family Data Sheet (Rev. B. 10/00) |

| ADSP-21060LCB-133 | 功能描述:IC DSP CONTROLLER 32BIT 225BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

| ADSP-21060LCBZ-133 | 功能描述:IC DSP CONTROLLER 32BIT 225PBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - DSP(數字式信號處理器) 系列:SHARC® 標準包裝:2 系列:StarCore 類型:SC140 內核 接口:DSI,以太網,RS-232 時鐘速率:400MHz 非易失內存:外部 芯片上RAM:1.436MB 電壓 - 輸入/輸出:3.30V 電壓 - 核心:1.20V 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:431-BFBGA,FCBGA 供應商設備封裝:431-FCPBGA(20x20) 包裝:托盤 |

發布緊急采購,3分鐘左右您將得到回復。