- 您現(xiàn)在的位置:買賣IC網 > PDF目錄374033 > ADSP-21365SBBC-ENG (ANALOG DEVICES INC) SHARC Processor PDF資料下載

參數(shù)資料

| 型號: | ADSP-21365SBBC-ENG |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | SHARC Processor |

| 中文描述: | 16-BIT, 55.55 MHz, OTHER DSP, PBGA136 |

| 封裝: | MO-205AE, MBGA-136 |

| 文件頁數(shù): | 11/54頁 |

| 文件大小: | 559K |

| 代理商: | ADSP-21365SBBC-ENG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

ADSP-21365/6

Preliminary Technical Data

Rev. PrA

|

Page 11 of 54

|

September 2004

PIN FUNCTION DESCRIPTIONS

ADSP-21365/6 pin definitions are listed below. Inputs identified

as synchronous (S) must meet timing requirements with respect

to CLKIN (or with respect to TCK for TMS and TDI). Inputs

identified as asynchronous (A) can be asserted asynchronously

to CLKIN (or to TCK for TRST). Tie or pull unused inputs to

V

DDEXT

or GND, except for the following:

DAI_Px, SPICLK, MISO, MOSI, EMU, TMS, TRST, TDI,

and AD15–0 (NOTE: These pins have pullup resistors.)

The following symbols appear in the Type column of

Table 3

:

A = Asynchronous, G = Ground, I = Input, O = Output,

P = Power Supply, S = Synchronous, (A/D) = Active Drive,

(O/D) = Open Drain, and T = Three-State , (pd) = pulldown

resistor, (pu) = pullup resistor.

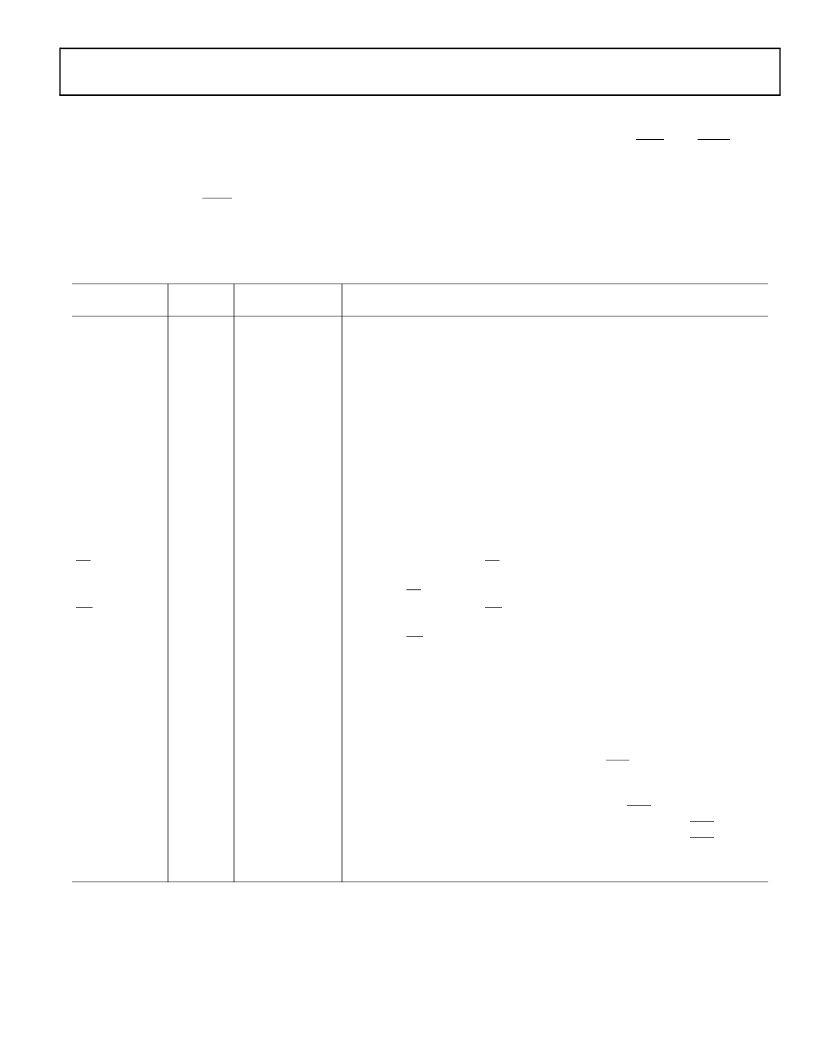

Table 3. Pin Descriptions

Pin

Type

State During and

After Reset

Three-state with

pullup enabled

Function

AD15–0

I/O/T

(pu)

Parallel Port Address/Data.

The ADSP-21365/6 parallel port and its corresponding

DMA unit output addresses and data for peripherals on these multiplexed pins. The

multiplex state is determined by the ALE pin. The parallel port can operate in either

8-bit or 16-bit mode. Each AD pin has a 22.5 k

internal pullup resistor. See

Address

Data Modes on page 14

for details of the AD pin operation.

For 8-bit mode: ALE is automatically asserted whenever a change occurs in the upper

16 external address bits, A23–8; ALE is used in conjunction with an external latch to

retain the values of the A23–8.

For 16-bit mode: ALE is automatically asserted whenever a change occurs in the

address bits, A15–0; ALE is used in conjunction with an external latch to retain the

values of the A15–0. To use these pins as flags (FLAGS15–0) or PWMs (PWM15–0), 1)

set (=1) bit 20 of the SYSCTL register to disable the parallel port, 2) set (=1) bits 22–25

of the SYSCTL register to enable FLAGS in groups of four (bit 22 for FLAGS3–0, bit 23

for FLAGS7–4 etc.) or, set (=1) bits 26–29 of the SYSCTL register to enable PWMs in

groups of four (bit 26 for PWM0–3, bit 27 for PWM4–7, and so on). When used as an

input, the IDP Channel 0 can use these pins for parallel input data.

Parallel Port Read Enable.

RD is asserted low whenever the processor reads 8-bit or

16-bit data from an external memory device. When AD15–0 are flags, this pin remains

deasserted. RD has a 22.5 k

internal pullup resistor.

Parallel Port Write Enable.

WR is asserted low whenever the processor writes 8-bit or

16-bit data to an external memory device. When AD15–0 are flags, this pin remains

deasserted. WR has a 22.5 k

internal pullup resistor.

Parallel Port Address Latch Enable.

ALE is asserted whenever the processor drives

a new address on the parallel port address pins. On reset, ALE is active high. However,

it can be reconfigured using software to be active low. When AD15–0 are flags, this

pin remains deasserted. ALE has a 20 k

internal pulldown resistor.

Flag Pins.

Each flag pin is configured via control bits as either an input or output. As

an input, it can be tested as a condition. As an output, it can be used to signal external

peripherals. These pins can be used as an SPI interface slave select output during SPI

mastering. These pins are also multiplexed with the IRQx and the TIMEXP signals.

In SPI master boot mode, FLAG0 is the slave select pin that must be connected to an

SPI EPROM. FLAG0 is configured as a slave select during SPI master boot. When bit 16

is set (=1) in the SYSCTL register, FLAG0 is configured as IRQ0.

When bit 17 is set (=1) in the SYSCTL register, FLAG1 is configured as IRQ1.

When bit 18 is set (=1) in the SYSCTL register, FLAG2 is configured as IRQ2.

When bit 19 is set (=1) in the SYSCTL register, FLAG3 is configured as TIMEXP which

indicates that the system timer has expired.

RD

O

(pu)

Three-state, driven

high

1

WR

O

(pu)

Three-state, driven

high

1

ALE

O

(pd)

Three-state, driven

low

1

FLAG3–0

I/O/A

Three-state

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21365SBBCZENG | SHARC Processor |

| ADSP-21365SBSQ-ENG | SHARC Processor |

| ADSP-21365SKBCZENG | SHARC Processor |

| ADSP-21365SKSQZENG | SHARC Processor |

| ADSP-21366SKBCZENG | SHARC Processor |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-21365SBBCZENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21365SBSQ-ENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21365SBSQZENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21365SCSQ-ENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21365SCSQZENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復。