- 您現在的位置:買賣IC網 > PDF目錄374037 > ADSP-2195MBST-140X (ANALOG DEVICES INC) DSP Microcomputer PDF資料下載

參數資料

| 型號: | ADSP-2195MBST-140X |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理 |

| 英文描述: | DSP Microcomputer |

| 中文描述: | 16-BIT, 160 MHz, OTHER DSP, PQFP144 |

| 封裝: | METRIC, PLASTIC, LQFP-144 |

| 文件頁數: | 9/68頁 |

| 文件大小: | 951K |

| 代理商: | ADSP-2195MBST-140X |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

This information applies to a product under development. Its characteristics and specifications are subject to change with-

out notice. Analog Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing.

9

REV. PrA

For current information contact Analog Devices at 800/262-5643

ADSP-2195

September 2001

priority level of 11 are aliased to the lowest priority bit

position (15) in these registers and share vector address

0x00 01E0.

Interrupt routines can either be nested with higher priority

interrupts taking precedence or processed sequentially.

Interrupts can be masked or unmasked with the IMASK

register. Individual interrupt requests are logically ANDed

with the bits in IMASK; the highest priority unmasked

interrupt is then selected. The emulation, power-down, and

reset interrupts are nonmaskable with the IMASK register,

but software can use the DIS INT instruction to mask the

power-down interrupt.

The Interrupt Control (ICNTL) register controls interrupt

nesting and enables or disables interrupts globally. The gen-

eral-purpose Programmable Flag (PFx) pins can be

configured as outputs, can implement software interrupts,

and (as inputs) can implement hardware interrupts. Pro-

grammable Flag pin interrupts can be configured for

level-sensitive, single edge-sensitive, or dual edge-

sensitive operation.

The IRPTL register is used to force and clear interrupts.

On-chip stacks preserve the processor status and are auto-

matically maintained during interrupt handling. To support

interrupt, loop, and subroutine nesting, the PC stack is

33 levels deep, the loop stack is eight levels deep, and the

status stack is 16 levels deep. To prevent stack overflow, the

PC stack can generate a stack-level interrupt if the PC stack

falls below three locations full or rises above 28

locations full.

The following instructions globally enable or disable

interrupt servicing, regardless of the state of IMASK.

ENA INT;

DIS INT;

At reset, interrupt servicing is disabled.

For quick servicing of interrupts, a secondary set of DAG

and computational registers exist. Switching between the

primary and secondary registers lets programs quickly

service interrupts, while preserving the DSP’s state.

DMA Controller

The ADSP-2195 has a DMA controller that supports

automated data transfers with minimal overhead for the

DSP core. Cycle stealing DMA transfers can occur between

the ADSP-2195’s internal memory and any of its

DMA-capable peripherals. Additionally, DMA transfers

can be accomplished between any of the DMA-capable

peripherals and external devices connected to the external

memory interface. DMA-capable peripherals include the

Host port, SPORTs, SPI ports, and UART. Each individual

DMA-capable peripheral has a dedicated DMA channel. To

describe each DMA sequence, the DMA controller uses a

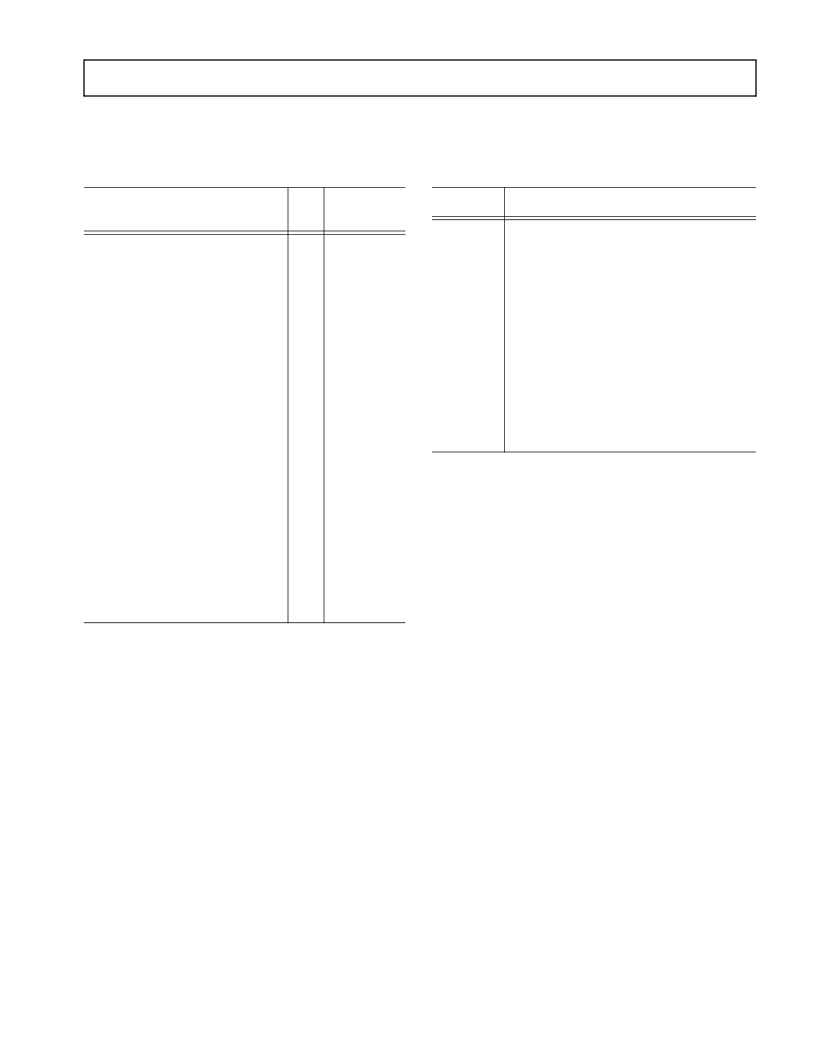

Table 2. Peripheral Interrupts and Priority at Reset

Interrupt

ID

Reset

Priority

Slave DMA/Host Port Interface

0

0

SPORT0 Receive

1

1

SPORT0 Transmit

2

2

SPORT1 Receive

3

3

SPORT1 Transmit

4

4

SPORT2 Receive/SPI0

5

5

SPORT2 Transmit/SPI1

6

6

UART Receive

7

7

UART Transmit

8

8

Timer A

9

9

Timer B

10

10

Timer C

11

11

Programmable Flag 0 (any PFx)

12

11

Programmable Flag 1 (any PFx)

13

11

Memory DMA port

14

11

Table 3. Interrupt Control (ICNTL) Register Bits

Bit

Description

0–3

Reserved

4

Interrupt Nesting Enable

5

Global Interrupt Enable

6

Reserved

7

MAC-Biased Rounding Enable

8–9

Reserved

10

PC Stack Interrupt Enable

11

Loop Stack Interrupt Enable

12–15

Reserved

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-2195 | LM2991 Negative Low Dropout Adjustable Regulator; Package: CERDIP; No of Pins: 16; Qty per Container: 25; Container: Rail |

| ADSP-2195MBCA-140X | LM2991 Negative Low Dropout Adjustable Regulator; Package: CERDIP; No of Pins: 16; Container: Rail |

| ADSP-2195MKST-160X | LM2991 Negative Low Dropout Adjustable Regulator; Package: TO-263; No of Pins: 5; Qty per Container: 45; Container: Rail |

| ADSP-2196 | DSP Microcomputer |

| ADSP-2196MBCA-140X | DSP Microcomputer |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-2195MKCA-160 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 24-Bit 160MHz 160MIPS 144-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述:16-BIT,160 MIPS, 2.5V, 80KBYTES RAM - Bulk |

| ADSP-2195MKST-160 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 24-Bit 160MHz 160MIPS 144-Pin LQFP 制造商:Analog Devices 功能描述:IC MICROCOMPUTER 16-BIT |

| adsp-2196mbca-140 | 制造商:Analog Devices 功能描述: |

| adsp-2196mbst-140 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 140MHz 140MIPS 144-Pin LQFP 制造商:Rochester Electronics LLC 功能描述: |

| ADSP-2196MBST-140Z | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 140MHz 140MIPS 144-Pin LQFP |

發布緊急采購,3分鐘左右您將得到回復。