- 您現在的位置:買賣IC網 > PDF目錄374039 > ADUC842BCP62-3 (ANALOG DEVICES INC) MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU PDF資料下載

參數資料

| 型號: | ADUC842BCP62-3 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

| 中文描述: | 8-BIT, FLASH, 8.38 MHz, MICROCONTROLLER, QCC56 |

| 封裝: | 8 X 8 MM, LEAD FRAME, MO-220VLLD2, CSP-56 |

| 文件頁數: | 21/88頁 |

| 文件大小: | 903K |

| 代理商: | ADUC842BCP62-3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

ADuC841/ADuC842/ADuC843

ACCUMULATOR SFR (ACC)

ACC is the accumulator register and is used for math opera-

tions including addition, subtraction, integer multiplication and

division, and Boolean bit manipulations. The mnemonics for

accumulator-specific instructions refer to the accumulator as A.

B SFR (B)

The B register is used with the ACC for multiplication and

division operations. For other instructions, it can be treated as a

general-purpose scratchpad register.

Stack Pointer (SP and SPH)

The SP SFR is the stack pointer and is used to hold an internal

RAM address that is called the top of the stack. The SP register

is incremented before data is stored during PUSH and CALL

executions. While the stack may reside anywhere in on-chip

RAM, the SP register is initialized to 07H after a reset, which

causes the stack to begin at location 08H.

Rev. 0 | Page 21 of 88

As mentioned earlier, the parts offer an extended 11-bit stack

pointer. The 3 extra bits used to make up the 11-bit stack

pointer are the 3 LSBs of the SPH byte located at B7H.

Data Pointer (DPTR)

The data pointer is made up of three 8-bit registers named DPP

(page byte), DPH (high byte), and DPL (low byte). These are

used to provide memory addresses for internal and external

code access and for external data access. They may be manipu-

lated as a 16-bit register (DPTR = DPH, DPL), although INC

DPTR instructions automatically carry over to DPP, or as three

independent 8-bit registers (DPP, DPH, DPL). The parts support

dual data pointers. Refer to the Dual Data Pointer section.

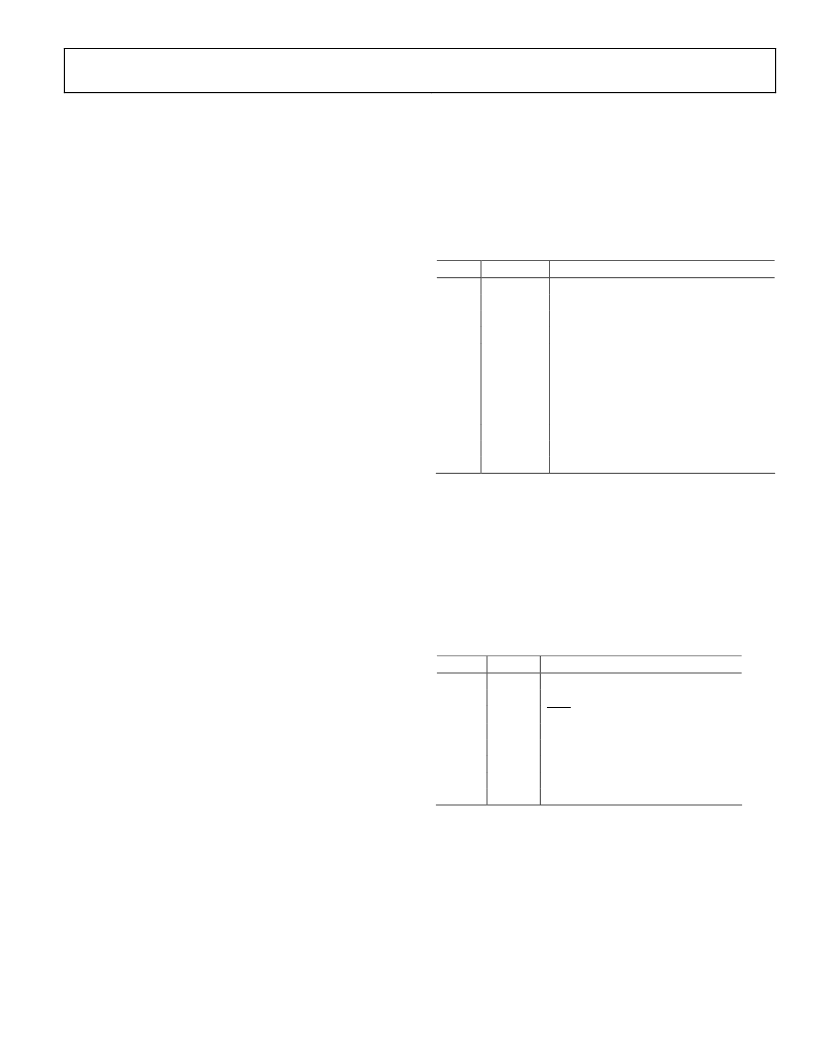

Program Status Word (PSW)

The PSW SFR contains several bits reflecting the current status

of the CPU, as detailed in Table 5.

SFR Address

Power-On Default

Bit Addressable

Table 5. PSW SFR Bit Designations

Bit

Name

7

CY

6

AC

5

F0

4

RS1

3

RS0

D0H

00H

Yes

Description

Carry Flag.

Auxiliary Carry Flag.

General-Purpose Flag.

Register Bank Select Bits.

RS1

0

0

1

1

1

Overflow Flag.

General-Purpose Flag.

Parity Bit.

RS0

0

1

0

Selected Bank

0

1

2

3

2

1

0

OV

F1

P

Power Control SFR (PCON)

The PCON SFR contains bits for power-saving options and

general-purpose status flags, as shown in Table 6.

SFR Address

Power-On Default

Bit Addressable

Table 6. PCON SFR Bit Designations

Bit No.

Name

7

SMOD

6

SERIPD

5

INT0PD

4

ALEOFF

3

GF1

2

GF0

1

PD

0

IDL

87H

00H

No

Description

Double UART Baud Rate.

I

2

C/SPI Power-Down Interrupt Enable.

INT0 Power-Down Interrupt Enable.

Disable ALE Output.

General-Purpose Flag Bit.

General-Purpose Flag Bit.

Power-Down Mode Enable.

Idle Mode Enable.

相關PDF資料 |

PDF描述 |

|---|---|

| ADUC843BCP62-5 | MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

| ADUC842BCP62-5 | MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

| ADUC843BCP62-3 | MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

| ADUC842BCP32-3 | MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

| ADUC843BCP32-3 | MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62-kB Flash MCU |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADUC842BCP62-3U | 制造商:Analog Devices 功能描述:MICROCONVERTER 1-CYCLE VERSION ADUC833 - Trays |

| ADUC842BCP62-3-U2 | 制造商:Analog Devices 功能描述:MICROCONVERTER 1-CYCLE VERSION ADUC834 - Trays |

| ADUC842BCP62-5 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| ADUC842BCP8-3 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| ADUC842BCP8-5 | 制造商:Analog Devices 功能描述:MCU 8-Bit ADuC8xx 8052 CISC 62KB Flash 5V 56-Pin LFCSP EP |

發布緊急采購,3分鐘左右您將得到回復。