- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374045 > ADV7123JST330 (ANALOG DEVICES INC) CMOS, 240 MHz Triple 10-Bit High Speed Video DAC PDF資料下載

參數(shù)資料

| 型號: | ADV7123JST330 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | DAC |

| 英文描述: | CMOS, 240 MHz Triple 10-Bit High Speed Video DAC |

| 中文描述: | PARALLEL, WORD INPUT LOADING, 10-BIT DAC, PQFP48 |

| 封裝: | PLASTIC, LQFP-48 |

| 文件頁數(shù): | 9/20頁 |

| 文件大小: | 342K |

| 代理商: | ADV7123JST330 |

ADV7123

–9–

REV. B

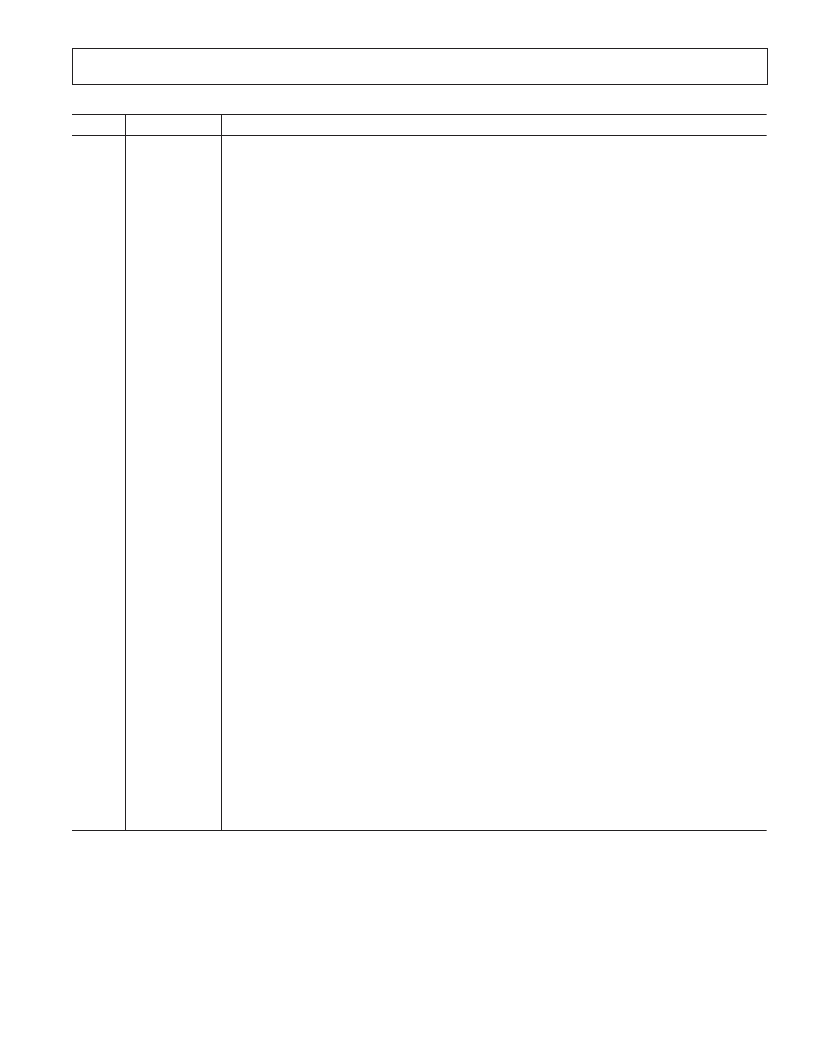

PIN FUNCTION DESCRIPTIONS

Pin No.

Mnemonic

Function

1–10

G0–G9

R0, G0, and B0 are the least significant data bits. Unused pixel data inputs should be connected to

either the regular PCB power or ground plane.

Composite Blank Control Input (TTL Compatible). A logic zero on this control input drives the analog

outputs, IOR, IOB, and IOG, to the blanking level. The

BLANK

signal is latched on the rising edge

of CLOCK. While

BLANK

is a logical zero, the R0–R9, G0–G9, and B0–B9 pixel inputs are ignored.

Composite Sync Control Input (TTL Compatible). A logical zero on the

SYNC

input switches off a

40 IRE current source. This is internally connected to the IOG analog output.

SYNC

does not over-

ride any other control or data input; therefore, it should only be asserted during the blanking interval.

SYNC

is latched on the rising edge of CLOCK.

If sync information is not required on the green channel, the

SYNC

input should be tied to logical zero.

Analog Power Supply (5 V

±

5%). All V

AA

pins on the ADV7123 must be connected.

R0, G0, and B0 are the least significant data bits. Unused pixel data inputs should be connected to

either the regular PCB power or ground plane.

Clock Input (TTL Compatible). The rising edge of CLOCK latches the R0–R9, G0–G9, B0–B9,

SYNC,

and

BLANK

pixel and control inputs. It is typically the pixel clock rate of the video system.

CLOCK should be driven by a dedicated TTL buffer.

Ground. All GND pins must be connected.

Differential Red, Green, and Blue Current Outputs (High Impedance Current Sources). These RGB

video outputs are specified to directly drive RS-343A and RS-170 video levels into a doubly terminated

75

load. If the complementary outputs are not required, these outputs should be tied to ground.

Red, Green, and Blue Current Outputs. These high impedance current sources are capable of directly

driving a doubly terminated 75

coaxial cable. All three current outputs should have similar output

loads whether or not they are all being used.

Compensation Pin. This is a compensation pin for the internal reference amplifier. A 0.1

μ

F ceramic

capacitor must be connected between COMP and V

AA

.

Voltage Reference Input for DACs or Voltage Reference Output (1.235 V)

A resistor (R

SET

) connected between this pin and GND controls the magnitude of the full-scale video

signal. Note that the IRE relationships are maintained, regardless of the full-scale output current. For

nominal video levels into a doubly terminated 75

load, R

SET

= 530

.

The relationship between R

SET

and the full-scale output current on IOG (assuming I

SYNC

is connected

to IOG) is given by:

R

SET

(

)

= 11,445

×

V

REF

(V)/IOG (mA)

The relationship between R

SET

and the full-scale output current on IOR, IOG, and IOB is given by:

IOG (mA)

= 11,445

×

V

REF

(V)/R

SET

(

) (

SYNC

being asserted)

IOR, IOB (mA)

= 7,989.6

×

V

REF

(V)/R

SET

(

)

The equation for IOG will be the same as that for IOR and IOB when

SYNC

is not being used, i.e.,

SYNC

tied permanently low.

Power Save Control Pin. Reduced power consumption is available on the ADV7123 when this pin is active.

Red, Green, and Blue Pixel Data Inputs (TTL Compatible). Pixel data is latched on the rising edge of

CLOCK.

11

BLANK

12

SYNC

13, 29, 30 V

AA

14–23

B0–B9

24

CLOCK

25, 26

27, 31, 33

GND

IOB

,

IOG

,

IOR

28, 32, 34 IOB, IOG, IOR

35

COMP

36

37

V

REF

R

SET

38

39–48

PSAVE

R0–R9

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7123JST240 | CMOS, 240 MHz Triple 10-Bit High Speed Video DAC |

| ADV7123 | CMOS, 240 MHz Triple 10-Bit High Speed Video DAC(240MHz三通道10位高速視頻D/A轉(zhuǎn)換器) |

| ADV7125JST240 | CMOS, 330 MHz Triple 8-Bit High Speed Video DAC |

| ADV7125JST330 | CMOS, 330 MHz Triple 8-Bit High Speed Video DAC |

| ADV7125 | CMOS, 330 MHz Triple 8-Bit High Speed Video DAC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7123JSTZ240 | 功能描述:IC DAC VIDEO TRPL HI SPD 48-LQFP RoHS:是 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 數(shù)模轉(zhuǎn)換器 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:50 系列:- 設置時間:4µs 位數(shù):12 數(shù)據(jù)接口:串行 轉(zhuǎn)換器數(shù)目:2 電壓電源:單電源 功率耗散(最大):- 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:8-TSSOP,8-MSOP(0.118",3.00mm 寬) 供應商設備封裝:8-uMAX 包裝:管件 輸出數(shù)目和類型:2 電壓,單極 采樣率(每秒):* 產(chǎn)品目錄頁面:1398 (CN2011-ZH PDF) |

| ADV7123JSTZ240 | 制造商:Analog Devices 功能描述:D/A Converter (D-A) IC |

| ADV7123JSTZ240-RL | 功能描述:IC DAC VIDEO 3-CH 240MHZ 48LQFP RoHS:是 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 數(shù)模轉(zhuǎn)換器 系列:- 標準包裝:47 系列:- 設置時間:2µs 位數(shù):14 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:1 電壓電源:單電源 功率耗散(最大):55µW 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:28-SSOP(0.209",5.30mm 寬) 供應商設備封裝:28-SSOP 包裝:管件 輸出數(shù)目和類型:1 電流,單極;1 電流,雙極 采樣率(每秒):* |

| ADV7123JSTZ240TMP | 制造商:Analog Devices 功能描述: |

| ADV7123JSTZ330 | 功能描述:IC DAC VIDEO 3CH 330MHZ 48-LQFP RoHS:是 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 數(shù)模轉(zhuǎn)換器 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:50 系列:- 設置時間:4µs 位數(shù):12 數(shù)據(jù)接口:串行 轉(zhuǎn)換器數(shù)目:2 電壓電源:單電源 功率耗散(最大):- 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:8-TSSOP,8-MSOP(0.118",3.00mm 寬) 供應商設備封裝:8-uMAX 包裝:管件 輸出數(shù)目和類型:2 電壓,單極 采樣率(每秒):* 產(chǎn)品目錄頁面:1398 (CN2011-ZH PDF) |

發(fā)布緊急采購,3分鐘左右您將得到回復。