- 您現在的位置:買賣IC網 > PDF目錄374047 > ADV7194KST (ANALOG DEVICES INC) Professional Extended-10⑩ Video Encoder with 54 MHz Oversampling PDF資料下載

參數資料

| 型號: | ADV7194KST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 顏色信號轉換 |

| 英文描述: | Professional Extended-10⑩ Video Encoder with 54 MHz Oversampling |

| 中文描述: | COLOR SIGNAL ENCODER, PQFP80 |

| 封裝: | LQFP-80 |

| 文件頁數: | 37/69頁 |

| 文件大小: | 647K |

| 代理商: | ADV7194KST |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

ADV7194

–37–

REV. 0

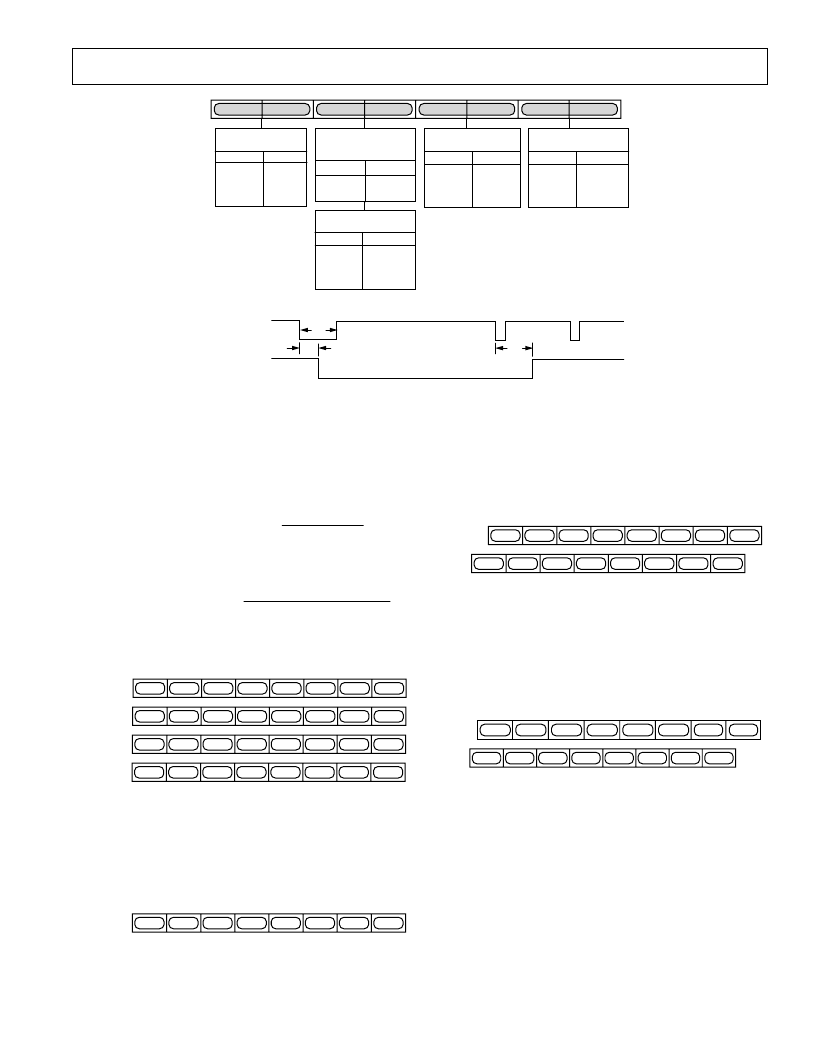

SUBCARRIER FREQUENCY REGISTERS 3–0

(FSC31–FSC0) (Address (SR4–SR0) = 0CH–0FH)

These 8-bit-wide registers are used to set up the Subcarrier Fre-

quency. The value of these registers are calculated by using the

following equation:

Register

=

(

Subcarrier Frequency

f

f

SCF

CLK

)

×

2

1

32

–

Example

:

NTSC Mode, f

CLK

= 27

MHz

,

f

SCF

= 3.5795454

MHz

=

(

Subcarrier Frequency

alue

V

)

×

×

×

2

1

3 5795454

.

10

27

10

32

6

6

–

Subcarrier Register Value = 21F07C16 Hex

Figure 68 shows how the frequency is set up by the four registers.

FSC31

FSC30

FSC29

FSC28

FSC27

FSC26

FSC25

FSC24

SUBCARRIER

FREQUENCY

REG 3

FSC23

FSC22

FSC21

FSC20

FSC19

FSC18

FSC17

FSC16

SUBCARRIER

FREQUENCY

REG 2

SUBCARRIER

FREQUENCY

REG 1

FSC7

FSC6

FSC5

FSC4

FSC3

FSC2

FSC1

FSC0

SUBCARRIER

FREQUENCY

REG 0

FSC15

FSC14

FSC13

FSC12

FSC11

FSC10

FSC9

FSC8

Figure 68. Subcarrier Frequency Registers

SUBCARRIER PHASE REGISTER (FPH7–FPH0)

(Address (SR4–SR0) = 10H)

This 8-bit-wide register is used to set up the Subcarrier Phase.

Each bit represents 1.41

°

. For normal operation this register is

set to 00Hex.

FPH7

FPH6

FPH5

FPH4

FPH3

FPH2

FPH1

FPH0

SUBCARRIER

PHASE

REGISTER

Figure 69. Subcarrier Phase Register

CLOSED CAPTIONING EVEN FIELD

DATA REGISTER 1–0 (CCD15–CCD00)

(Address (SR4–SR0) = 11–12H)

These 8-bit-wide registers are used to set up the closed captioning

extended data bytes on Even Fields. Figure 70 shows how the

high and low bytes are set up in the registers.

CCD15

CCD14

CCD13

CCD12

CCD11

CCD10

CCD9

CCD8

BYTE 1

CCD7

CCD6

CCD5

CCD4

CCD3

CCD2

CCD1

CCD0

BYTE 0

Figure 70. Closed Captioning Extended Data Register

CLOSED CAPTIONING ODD FIELD

DATA REGISTER 1–0 (CCD15–CCD0)

(Subaddress (SR4–SR0) = 13–14H)

These 8-bit-wide registers are used to set up the closed captioning

data bytes on Odd Fields. Figure 71 shows how the high and low

bytes are set up in the registers.

CCD15

BYTE 1

CCD7

CCD6

CCD5

CCD4

CCD3

CCD2

CCD1

CCD0

BYTE 0

CCD14

CCD13

CCD12

CCD11

CCD10

CCD9

CCD8

Figure 71. Closed Captioning Data Register

NTSC PEDESTAL/PAL TELETEXT CONTROL

REGISTERS 3–0

(PCE15–0, PCO15–0)/(TXE15–0, TXO15–0)

(Subaddress (SR4–SR0) = 15–18H)

These 8-bit-wide registers are used to enable the NTSC pedes-

tal/PAL Teletext on a line by line basis in the vertical blanking

interval for both odd and even

fi

elds. Figures 68 and 69 show

the four control registers. A Logic 1 in any of the bits of these

registers has the effect of turning the Pedestal OFF on the

equivalent line when used in NTSC. A Logic 1 in any of the

bits of these registers has the effect of turning Teletext ON on

the equivalent line when used in PAL.

TR17

TR16

TR15

TR14

TR13

TR12

TR11

TR10

TR17 TR16

0 0 0 T

PCLK

0

1

1

0

1

1

1 T

PCLK

2 T

PCLK

3 T

PCLK

HSYNC

TO PIXEL

DATA ADJUST

TR15 TR14 T

C

0 T

B

1

T

B

+ 32 s

HSYNC

TO

VSYNC

RISING EDGE DELAY

(MODE 1 ONLY)

TR13 TR12 T

B

0 0 0 T

PCLK

0

1

1

0

1

1

4 T

PCLK

8 T

PCLK

18 T

PCLK

HSYNC

TO

VSYNC

DELAY

TR11 TR10 T

A

0 0 1 T

PCLK

0

1

1

0

1

1

4 T

PCLK

16 T

PCLK

128 T

PCLK

HSYNC

WIDTH

TR15 TR14

0 0 1 T

PCLK

0

1

1

0

1

1

4 T

PCLK

16 T

PCLK

128 T

PCLK

VSYNC

WIDTH

(MODE 2 ONLY)

LINE 313

LINE 314

LINE 1

T

B

T

A

T

C

VSYNC

HSYNC

TIMING MODE 1 (MASTER/PAL)

Figure 67. Timing Register 1

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7194 | Professional Extended-10⑩ Video Encoder with 54 MHz Oversampling |

| ADV7202 | Simultaneous Sampling Video Rate Codec |

| ADV7300A | Multiformat SD, Progressive Scan/HDTV Video Encoder with Six NSV⑩ 12-Bit DACs |

| ADV7300AKST | Multiformat SD, Progressive Scan/HDTV Video Encoder with Six NSV⑩ 12-Bit DACs |

| ADV7301A | Multiformat SD, Progressive Scan/HDTV Video Encoder with Six NSV⑩ 12-Bit DACs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV7194KSTZ | 功能描述:IC ENCODER VIDEO EXT-10 80-LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 編碼器,解碼器,轉換器 系列:- 產品變化通告:Development Systems Discontinuation 26/Apr/2011 標準包裝:1 系列:- 類型:編碼器 應用:DVB-S.2 系統 電壓 - 電源,模擬:- 電壓 - 電源,數字:- 安裝類型:- 封裝/外殼:模塊 供應商設備封裝:模塊 包裝:散裝 其它名稱:Q4645799 |

| ADV7194KSTZ | 制造商:Analog Devices 功能描述:TV / Video IC |

| ADV7195 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs and 10-Bit Data Input |

| ADV7195KS | 制造商:Analog Devices 功能描述:Video Encoder 3DAC 11-Bit 52-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:MULTI-FORMAT VID+PROGSCAN/HDTV ENCODERIC - Bulk |

| ADV7195KST | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs and 10-Bit Data Input |

發布緊急采購,3分鐘左右您將得到回復。