- 您現在的位置:買賣IC網 > PDF目錄374047 > ADV7310KST (ANALOG DEVICES INC) Multiformat 216 MHz Video Encoder with Six NSV 12-Bit DACs PDF資料下載

參數資料

| 型號: | ADV7310KST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 顏色信號轉換 |

| 英文描述: | Multiformat 216 MHz Video Encoder with Six NSV 12-Bit DACs |

| 中文描述: | COLOR SIGNAL ENCODER, PQFP64 |

| 封裝: | PLASTIC, MS-026BCD, LQFP-64 |

| 文件頁數: | 53/84頁 |

| 文件大小: | 1099K |

| 代理商: | ADV7310KST |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁當前第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

REV. A

ADV7310/ADV7311

–53–

Coring Gain Border

[Address 63h, Bits 3–0]

These four bits are assigned to the gain factor applied to

border areas.

In DNR mode, the range of gain values is 0 to 1 in increments

of 1/8. This factor is applied to the DNR filter output, which

lies below the set threshold range. The result is then subtracted

from the original signal.

In DNR sharpness mode, the range of gain values is 0 to 0.5 in

increments of 1/16. This factor is applied to the DNR filter

output, which lies above the threshold range.

The result is added to the original signal.

Coring Gain Data

[Address 63h, Bits 7–4]

These four bits are assigned to the gain factor applied to the

luma data inside the MPEG pixel block.

In DNR mode, the range of gain values is 0 to 1 in increments

of 1/8. This factor is applied to the DNR filter output, which

lies below the set threshold range. The result is then subtracted

from the original signal.

In DNR sharpness mode, the range of gain values is 0 to 0.5 in

increments of 1/16. This factor is applied to the DNR filter

output, which lies above the threshold range.

The result is added to the original signal.

O X X X X X X O O X X X X X X O

O X X X X X X O O X X X X X X O

O X X X X X X O O X X X X X X O

DNR27 – DNR24 = 01h

OFFSET CAUSED

BY VARIATIONS IN

INPUT TIMING

APPLY BORDER

CORING GAIN

APPLY DATA

CORING GAIN

Figure 49. DNR Offset Control

DNR Threshold

[Address 64h, Bits 5–0]

These six bits are used to define the threshold value in the range

of 0 to 63. The range is an absolute value.

Border Area

[Address 64h, Bit 6]

When this bit is set to a Logic 1, the block transition area can be

defined to consist of four pixels. If this bit is set to a Logic 0,

the border transition area consists of two pixels, where one pixel

refers to two clock cycles at 27 MHz.

720 485 PIXELS

(NTSC)

8 8 PIXEL BLOCK

8 8 PIXEL BLOCK

2-PIXEL

BORDER DATA

Figure 50. DNR Border Area

Block Size Control

[Address 64h, Bit 7]

This bit is used to select the size of the data blocks to be pro-

cessed. Setting the block size control function to a Logic 1 defines

a 16 pixel

×

16 pixel data block, and a Logic 0 defines an 8 pixel

×

8 pixel data block, where one pixel refers to two clock cycles

at 27 MHz.

DNR Input Select Control

[Address 65h, Bit 2–0]

Three bits are assigned to select the filter, which is applied to

the incoming Y data. The signal that lies in the pass band of

the selected filter is the signal that will be DNR processed.

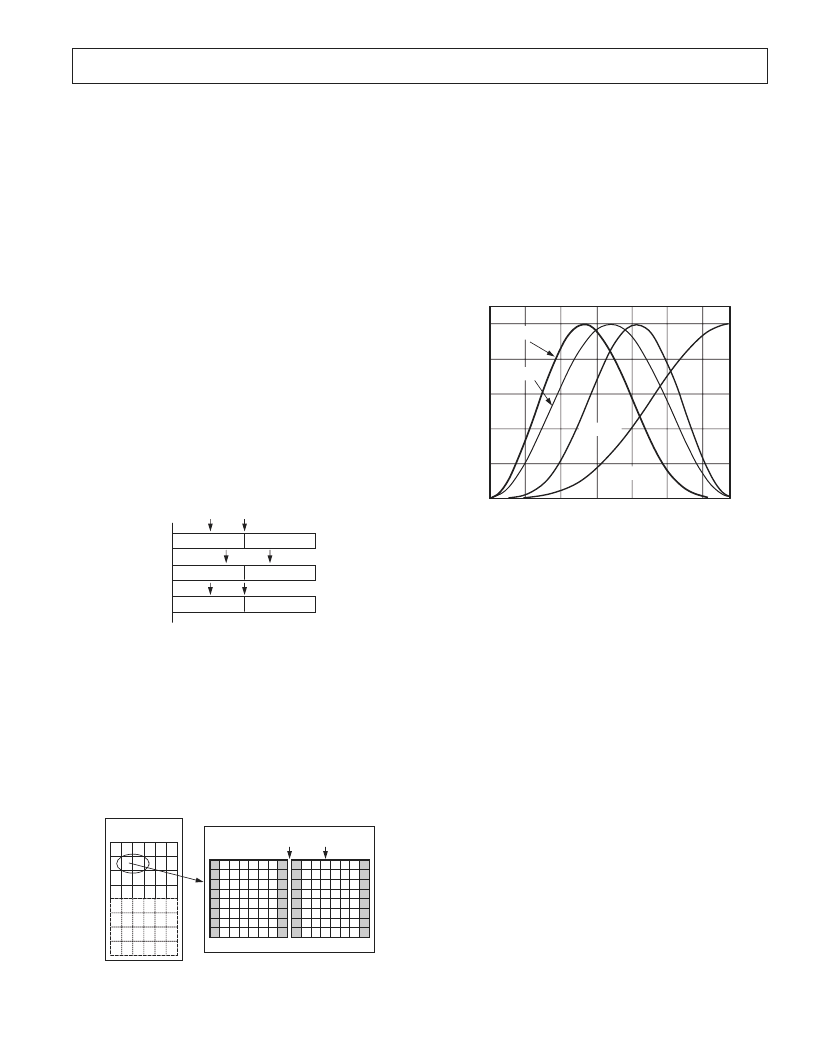

Figure 51 shows the filter responses selectable with this control.

FILTER C

FILTER B

FILTER A

FILTER D

FREQUENCY (Hz)

00

1

2

3

4

5

6

0.2

0.4

0.6

M

0.8

1.0

Figure 51. DNR Input Select

DNR Mode Control

[Address 65h, Bit 4]

This bit controls the DNR mode selected. A Logic 0 selects

DNR mode; a Logic 1 selects DNR sharpness mode.

DNR works on the principle of defining low amplitude, high

frequency signals as probable noise and subtracting this noise

from the original signal.

In DNR mode, it is possible to subtract a fraction of the signal

that lies below the set threshold, assumed to be noise, from the

original signal. The threshold is set in DNR Register 1.

When DNR sharpness mode is enabled, it is possible to add a

fraction of the signal that lies above the set threshold to the

original signal, since this data is assumed to be valid data and

not noise. The overall effect is that the signal will be boosted

(similar to using Extended SSAF filter).

Block Offset Control

[Address 65h, Bits 7–4]

Four bits are assigned to this control, which allows a shift of the

data block of 15 pixels maximum. Consider the coring gain posi-

tions fixed. The block offset shifts the data in steps of one pixel

such that the border coring gain factors can be applied at the

same position regardless of variations in input timing of the data.

相關PDF資料 |

PDF描述 |

|---|---|

| ADV7311 | Multiformat 216 MHz Video Encoder with Six NSV 12-Bit DACs |

| ADV7311KST | Multiformat 216 MHz Video Encoder with Six NSV 12-Bit DACs |

| ADV7312 | Multiformat 11-Bit HDTV Video Encoder |

| ADV7312KST | Multiformat 11-Bit HDTV Video Encoder |

| ADV7320KSTZ | Multiformat 216 MHz Video Encoder with Six NSV 12-Bit DACs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADV7310KSTZ | 制造商:Analog Devices 功能描述:VID ENCODER 6DAC 12-BIT 64LQFP - Bulk |

| ADV7311 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat 216 MHz Video Encoder with Six NSV 12-Bit DACs |

| ADV7311KST | 功能描述:IC VID ENC 6-12BIT DAC'S 64LQFP RoHS:否 類別:集成電路 (IC) >> 接口 - 編碼器,解碼器,轉換器 系列:- 產品變化通告:Development Systems Discontinuation 26/Apr/2011 標準包裝:1 系列:- 類型:編碼器 應用:DVB-S.2 系統 電壓 - 電源,模擬:- 電壓 - 電源,數字:- 安裝類型:- 封裝/外殼:模塊 供應商設備封裝:模塊 包裝:散裝 其它名稱:Q4645799 |

| ADV7311KST | 制造商:Analog Devices 功能描述:Video IC |

| ADV7312 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat 11-Bit HDTV Video Encoder |

發布緊急采購,3分鐘左右您將得到回復。