- 您現在的位置:買賣IC網 > PDF目錄379831 > CDC913 (Texas Instruments, Inc.) PC Motherboard Clock Sythesizer/Drivers with SDRAM Clock Support(PC母板時鐘發生器(帶雙1-4緩沖器和三態輸出)) PDF資料下載

參數資料

| 型號: | CDC913 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | PC Motherboard Clock Sythesizer/Drivers with SDRAM Clock Support(PC母板時鐘發生器(帶雙1-4緩沖器和三態輸出)) |

| 中文描述: | 電腦主板時鐘Sythesizer / SDRAM時鐘與支持(電腦母板時鐘發生器(帶雙1-4緩沖器和三態輸出驅動器)) |

| 文件頁數: | 1/9頁 |

| 文件大小: | 185K |

| 代理商: | CDC913 |

CDC913

PC MOTHERBOARD CLOCK GENERATOR

WITH DUAL 1-TO-4 BUFFERS AND 3-STATE OUTPUTS

SCAS502C – APRIL 1995 – REVISED MAY 1996

1

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

Generates Programmable CPU Clock

Output (50 MHz, 60 MHz, or 66 MHz)

Generates 33-MHz Clock for Asynchronous

PCI

One 14.318-MHz Reference Clock Output

All Output Clock Frequencies Derived From

a Single 14.31818-MHz Crystal Input

LVTTL-Compatible Inputs and Outputs

Internal Loop Filters for Phase-Lock Loops

Eliminate the Need for External

Components

Operates at 3.3-V V

CC

Package Options Include Plastic

Small-Outline (DW) and Shrink

Small-Outline (DB) Packages

description

The CDC913 is a high-performance clock generator with integrated dual 1-to-4 buffers, which simplifies clock

system design for PC motherboards. The CDC913 consists of a crystal oscillator, two phase-locked loops (PLL),

and two 1-to-4 buffers. The CDC913 generates all frequencies using a single 14.318-MHz crystal.

The CPUCLK output is programmable to one of three frequencies (50 MHz, 60 MHz, or 66 MHz) via the SEL0

and SEL1 inputs. PCICLK outputs a 33-MHz clock, independent of the CPUCLK frequency. REFCLK provides

a buffered copy of the 14.318-MHz reference. The oscillator and PLLs in the CDC913 are bypassed when in

the TEST mode, i.e., SEL1 = SEL0 = H. When in the TEST mode, a test clock can be driven over the X1 input

and buffered out from the PCICLK, CPUCLK, and REFCLK outputs.

Outputs 1Yn and 2Yn are 3-state outputs and are enabled via OE. When OE is high, the outputs are in the

high-impedance state. When OE is low, the outputs are enabled.

Since the CDC913 is based on PLL circuitry, it requires a stabilization time to achieve phase lock of the PLL.

This stabilization time is required following power up and application of a fixed-frequency, fixed-phase signal

at the X1 input, and following any changes to the SELn inputs.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

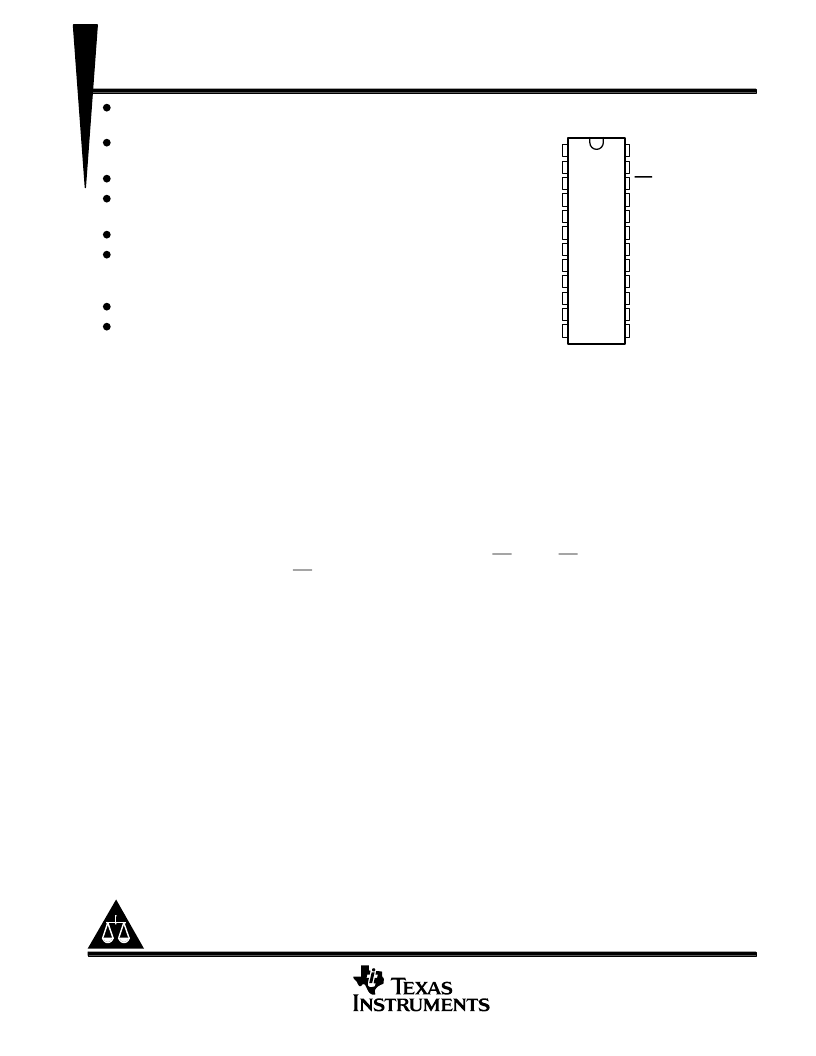

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

X1

X2

AGND

V

CC

1Y1

1Y2

1Y3

1Y4

GND

1A

CPUCLK

SEL0

A

VCC

REFCLK

OE

VCC

2Y1

2Y2

2Y3

2Y4

GND

2A

PCICLK

SEL1

DB OR DW PACKAGE

(TOP VIEW)

Copyright

1996, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

相關PDF資料 |

PDF描述 |

|---|---|

| CDC9161 | PC Motherboard Clock Sythesizer/Drivers with SDRAM Clock Support(PC母板時鐘合成器/驅動器(三態輸出)) |

| CDC9162 | PC Motherboard Clock Sythesizer/Drivers with SDRAM Clock Support(PC母板時鐘合成器/驅動器(三態輸出)) |

| CDC9163 | PC Motherboard Clock Sythesizer/Drivers with SDRAM Clock Support(PC時鐘合成器/驅動器(SDRAM 時鐘支持)) |

| CDC9171 | DVD System Clock Synthesizerers(DVD系統時鐘合成器) |

| CDC9441 | DVD System Clock Synthesizerers(PC時鐘合成器/驅動器(SDRAM 時鐘支持)) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| CDC913DB | 制造商:TI 制造商全稱:Texas Instruments 功能描述:PC MOTHERBOARD CLOCK GENERATOR WITH DUAL 1-TO-4 BUFFERS AND 3-STATE OUTPUTS |

| CDC913DW | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CDC913DWR | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CDC9161DL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CPU System Clock Generator |

| CDC921 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIRECT RAMBUSE CLOCK GENERATOR |

發布緊急采購,3分鐘左右您將得到回復。