- 您現在的位置:買賣IC網 > PDF目錄21998 > EP4CE75F23I8LN (Altera)IC CYCLONE IV E FPGA 75K 484FBGA PDF資料下載

參數資料

| 型號: | EP4CE75F23I8LN |

| 廠商: | Altera |

| 文件頁數: | 42/42頁 |

| 文件大小: | 0K |

| 描述: | IC CYCLONE IV E FPGA 75K 484FBGA |

| 產品培訓模塊: | Designing an IP Surveillance Camera Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview |

| 特色產品: | Cyclone? IV FPGAs |

| 標準包裝: | 60 |

| 系列: | CYCLONE® IV E |

| LAB/CLB數: | 4713 |

| 邏輯元件/單元數: | 75408 |

| RAM 位總計: | 2810880 |

| 輸入/輸出數: | 292 |

| 電源電壓: | 0.97 V ~ 1.03 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 484-BGA |

| 供應商設備封裝: | 484-FBGA(23x23) |

| 其它名稱: | 544-2678 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當前第42頁

Chapter 1: Cyclone IV Device Datasheet

1–9

Operating Conditions

December 2013

Altera Corporation

The OCT resistance may vary with the variation of temperature and voltage after

calibration at device power-up. Use Table 1–10 and Equation 1–1 to determine the

final OCT resistance considering the variations after calibration at device power-up.

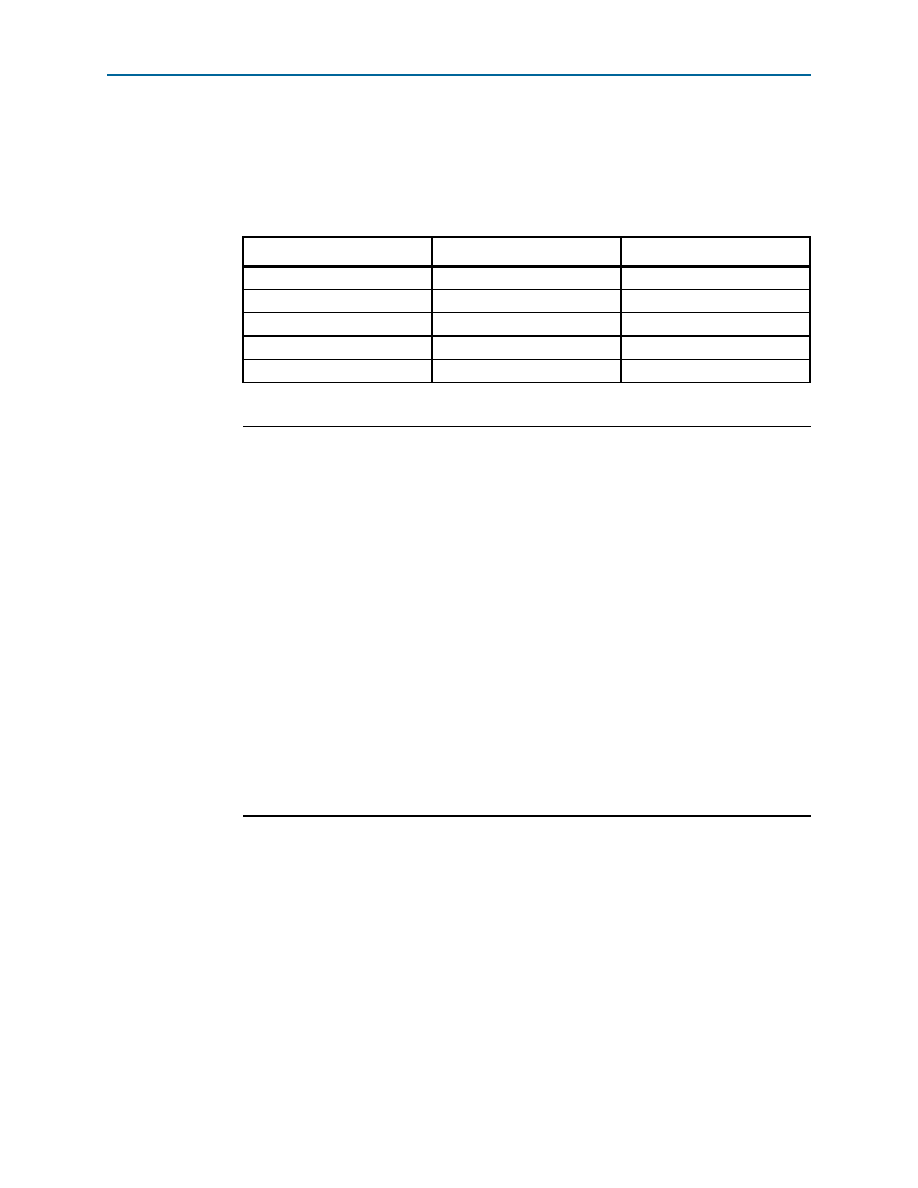

Table 1–10 lists the change percentage of the OCT resistance with voltage and

temperature.

Table 1–10. OCT Variation After Calibration at Device Power

-Up for Cyclone IV Devices

Nominal Voltage

dR/dT (%/°C)

dR/dV (%/mV)

3.0

0.262

–0.026

2.5

0.234

–0.039

1.8

0.219

–0.086

1.5

0.199

–0.136

1.2

0.161

–0.288

R

V = (V2 – V1) × 1000 × dR/dV –––––

R

T = (T2 – T1) × dR/dT –––––

For

R

x < 0; MFx = 1/ (|Rx|/100 + 1) –––––

Notes to Equation 1–1:

(1) T2 is the final temperature.

(2) T1 is the initial temperature.

(3) MF is multiplication factor.

(4) Rfinal is final resistance.

(5) Rinitial is initial resistance.

(6) Subscript x refers to both V and T.

(7)

R

V is a variation of resistance with voltage.

(8)

R

T is a variation of resistance with temperature.

(9) dR/dT is the change percentage of resistance with temperature after calibration at device power

-up.

(10) dR/dV is the change percentage of resistance with voltage after calibration at device power

-up.

(11) V2 is final voltage.

(12) V1 is the initial voltage.

相關PDF資料 |

PDF描述 |

|---|---|

| GCC06DRXH | CONN EDGECARD 12POS DIP .100 SLD |

| ESA50DTBT | CONN EDGECARD 100PS R/A .125 SLD |

| GBC08DRTS | CONN EDGECARD 16POS DIP .100 SLD |

| 7-1624112-5 | INDUCTOR 15NH 5% 0603 |

| EBC08DRYS | CONN EDGECARD 16POS DIP .100 SLD |

相關代理商/技術參數 |

參數描述 |

|---|---|

| EP4CE75F29C6 | 功能描述:FPGA - 現場可編程門陣列 FPGA - Cyclone IV E 4713 LABs 426 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE75F29C6N | 功能描述:FPGA - 現場可編程門陣列 FPGA - Cyclone IV E 4713 LABs 426 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE75F29C7 | 功能描述:FPGA - 現場可編程門陣列 FPGA - Cyclone IV E 4713 LABs 426 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE75F29C7N | 功能描述:FPGA - 現場可編程門陣列 FPGA - Cyclone IV E 4713 LABs 426 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP4CE75F29C8 | 功能描述:FPGA - 現場可編程門陣列 FPGA - Cyclone IV E 4713 LABs 426 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發布緊急采購,3分鐘左右您將得到回復。