- 您現在的位置:買賣IC網 > PDF目錄385336 > GS8662R18E-250 (GSI TECHNOLOGY) 72Mb SigmaCIO DDR-II Burst of 4 SRAM PDF資料下載

參數資料

| 型號: | GS8662R18E-250 |

| 廠商: | GSI TECHNOLOGY |

| 元件分類: | DRAM |

| 英文描述: | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| 中文描述: | 4M X 18 DDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 15 MM X 17 MM, 1MM PITCH, FPBGA-165 |

| 文件頁數: | 21/37頁 |

| 文件大小: | 942K |

| 代理商: | GS8662R18E-250 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

Preliminary

GS8662R08/09/18/36E-333/300/250/200/167

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

Rev: 1.01 9/2005

21/37

2005, GSI Technology

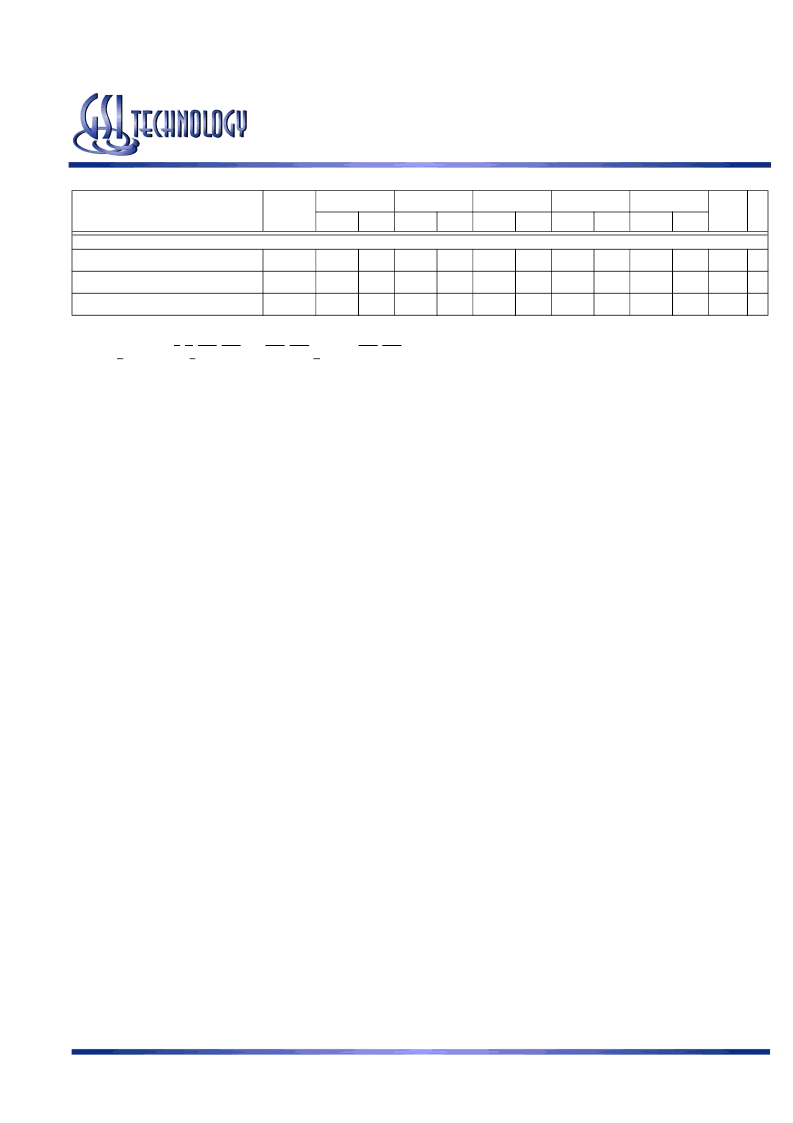

Hold Times

Address Input Hold Time

t

KHAX

0.4

—

0.4

—

0.5

—

0.6

—

0.7

—

ns

Control Input Hold Time

t

KHIX

0.4

—

0.4

—

0.5

—

0.6

—

0.7

—

ns

Data Input Hold Time

Notes:

1.

All Address inputs must meet the specified setup and hold times for all latching clock edges.

2.

Control singles are R, W, BW0, BW1, and (NW0, NW1 for x8) and (BW2, BW3 for x36).

3.

If C, C are tied high, K, K become the references for C, C timing parameters

4.

To avoid bus contention, at a given voltage and temperature tCHQX1 is bigger than tCHQZ. The specs as shown do not imply bus contention because tCHQX1 is a MIN

parameter that is worst case at totally different test conditions (0

°

C, 1.9 V) than tCHQZ, which is a MAX parameter (worst case at 70

°

C, 1.7 V). It is not possible for two

SRAMs on the same board to be at such different voltages and temperatures.

5.

Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.

6.

V

DD

slew rate must be less than 0.1 V DC per 50 ns for DLL lock retention. DLL lock time begins once V

DD

and input clock are stable.

7.

Echo clock is very tightly controlled to data valid/data hold. By design, there is a ±0.1 ns variation from echo clock to data. The datasheet parameters reflect tester guard

bands and test setup variations.

t

KHDX

0.28

—

0.3

—

0.35

—

0.4

—

0.5

—

ns

AC Electrical Characteristics (Continued)

Parameter

Symbol

-333

-300

-250

-200

-167

Units

N

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

相關PDF資料 |

PDF描述 |

|---|---|

| GS8662R18E-250I | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662R18E-300 | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662R18E-300I | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662R18E-333 | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662R18E-333I | 72Mb SigmaCIO DDR-II Burst of 4 SRAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| GS8662R18E-250I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662R18E-300 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662R18E-300I | 制造商:GSI Technology 功能描述:SRAM SYNC SGL 1.8V 72MBIT 4MX18 0.45NS 165FBGA - Trays |

| GS8662R18E-333 | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb SigmaCIO DDR-II Burst of 4 SRAM |

| GS8662R18E-333I | 制造商:GSI 制造商全稱:GSI Technology 功能描述:72Mb SigmaCIO DDR-II Burst of 4 SRAM |

發布緊急采購,3分鐘左右您將得到回復。