- 您現在的位置:買賣IC網 > PDF目錄385388 > HMP8116 (Intersil Corporation) NTSC/PAL Video Decoder PDF資料下載

參數資料

| 型號: | HMP8116 |

| 廠商: | Intersil Corporation |

| 英文描述: | NTSC/PAL Video Decoder |

| 中文描述: | NTSC / PAL視頻解碼器 |

| 文件頁數: | 12/43頁 |

| 文件大小: | 182K |

| 代理商: | HMP8116 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

12

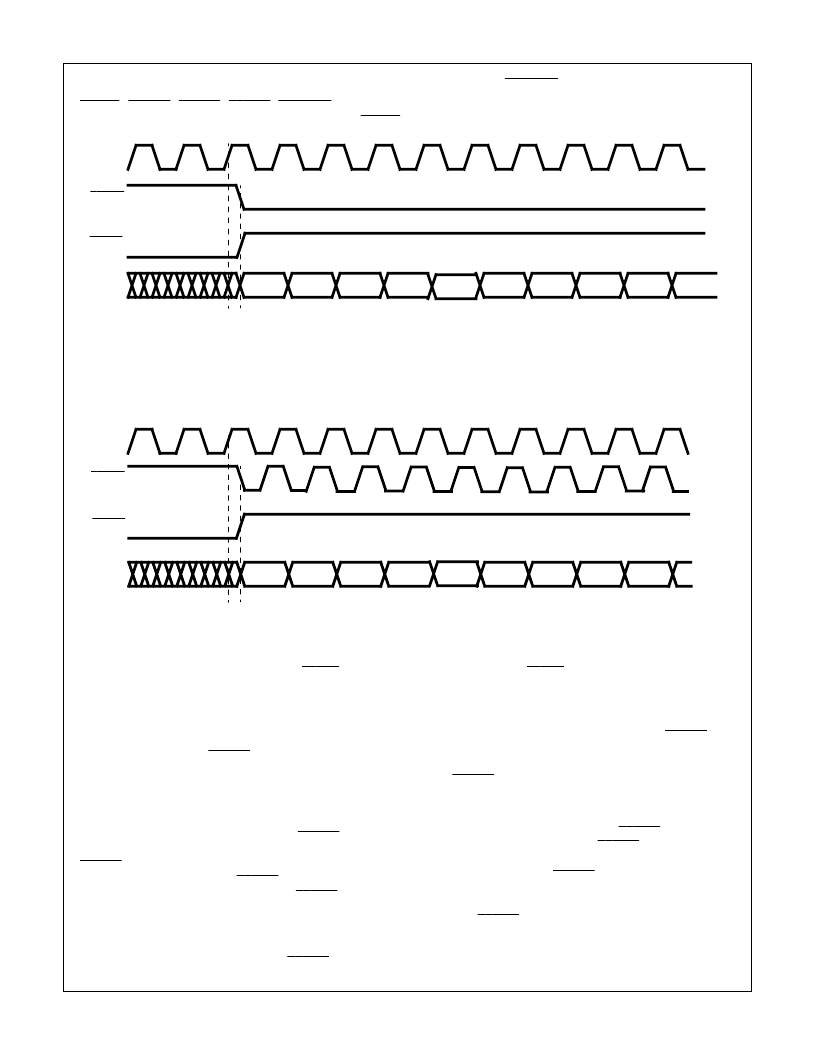

ures 9 and 10.

BLANK, HSYNC, VSYNC, DVALID, VBIVALID, and FIELD

are output following the rising edge of CLK2. When BLANK

is asserted and VBIVALID is deasserted, the YCbCr outputs

have a value of 16 for Y and 128 for Cb and Cr.

16-BIT YCbCr, 15-BIT RGB, OR 16-RGB OUTPUT

In these output modes, DVALID may be configured to oper-

ate in one of four modes as controlled by the DVLD_LTC and

DVLD_DCYC bits of the GENLOCK CONTROL register

(04

H

). Bit 4 is the DVLD_LTC bit and bit 5 is the

DVLD_DCYC bit.

If DVLD_LTC=0 and DVLD_DCYC=0 , DVALID is present

only during the active video time on active scan lines. Thus,

DVALID being asserted indicates valid pixel data is present

on the P0-P15 pixel outputs. DVALID is never asserted dur-

ing the blanking intervals. In this mode DVALID will have a

50% duty cycle only during the active video times. The tim-

ing diagrams for this mode can be found in figures 11 and

12.

If DVLD_LTC=0 and DVLD_DCYC=1, DVALID behaves the

same as the first mode, with the exception that DVALID does

not have a 50% duty cycle. This mode is intended for back-

ward compatibility with HMP8112(A) timing dependancies in

which DVALID did not have a 50% duty cycle timing and

other timing variations. The timing diagrams for this mode

can be found in figures 13 and 14.

If DVLD_LTC=1 and DVLD_DCYC=0, DVALID is present the

entire line time on all scan lines. DVALID may occasionally

be negated for two consecutive CLK2 cycles just prior to

active video. In this mode DVALID is guaranteed have a 50%

duty cycle only during the active video times. The timing for

this mode differs from the timing shown in figures 11 and 12

only in that DVALID will also be asserted during the blanking

portion of the video line time as described above.

NOTE:

9. Y

0

is the first active luminance pixel data of a line. Cb

0

and Cr

0

are first active chrominance pixel data in a line. Cb and Cr will alternate

every cycle due to the 4:2:2 subsampling. Pixel data is not output during the blanking period, but the values on the ports are forced to

blanking levels.

FIGURE 9. OUTPUT TIMING FOR 8-BIT YCbCr MODE (DVLD_LTC = 0)

CLK

DVALID

P[15-8]

t

DVLD

Cb

0

Y

0

Cr

0

Cb

2

Y

2

Cr

2

Y

1

Y

3

Cb

4

Y

4

BLANK

CLK

DVALID

P[15-8]

t

DVLD

Cb

0

Y

0

Cr

0

Cb

2

Y

2

Cr

2

Y

1

Y

3

Cb

4

NOTES:

10. Y

0

is the first active luminance pixel data of a line. Cb

0

and Cr

0

are first active chrominance pixel data in a line. Cb and Cr will alternate

every cycle due to the 4:2:2 subsampling. Pixel data is not output during the blanking period, but the values on the ports are forced to

blanking levels.

11. When DVLD_LTC is set to 1, the polarity of DVALID needs to be set to active low, otherwise DVALID will stay low during active video and

be gated with the clock only during the blanking interval.

FIGURE 10. OUTPUT TIMING FOR 8-BIT YCbCr MODE (DVLD_LTC = 1)

Y

4

BLANK

HMP8116

相關PDF資料 |

PDF描述 |

|---|---|

| HMP8116CN | NTSC/PAL Video Decoder |

| HMP8117 | NTSC/PAL Video Decoder |

| HMP8117CN | NTSC/PAL Video Decoder |

| HMP8154 | NTSC/PAL Encoders |

| HMP8154CN | NTSC/PAL Encoders |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HMP8116CN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8117 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8117_07 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8117CN | 功能描述:編碼器、解碼器、復用器和解復用器 80PQFP,0+70C NTSC/PAL VIDEO DECODER W/MA RoHS:否 制造商:Micrel 產品:Multiplexers 邏輯系列:CMOS 位數: 線路數量(輸入/輸出):2 / 12 傳播延遲時間:350 ps, 400 ps 電源電壓-最大:2.625 V, 3.6 V 電源電壓-最小:2.375 V, 3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-44 封裝:Tray |

| HMP8117CN96 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發布緊急采購,3分鐘左右您將得到回復。