- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361044 > LMX2301TMX (NATIONAL SEMICONDUCTOR CORP) PLLatinumTM 160 MHz Frequency Synthesizer for RF Personal Communications PDF資料下載

參數(shù)資料

| 型號(hào): | LMX2301TMX |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | PLLatinumTM 160 MHz Frequency Synthesizer for RF Personal Communications |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 160 MHz, PDSO20 |

| 封裝: | 0.173 INCH, PLASTIC, TSSOP-20 |

| 文件頁數(shù): | 11/14頁 |

| 文件大小: | 225K |

| 代理商: | LMX2301TMX |

Application Information

LOOP FILTER DESIGN

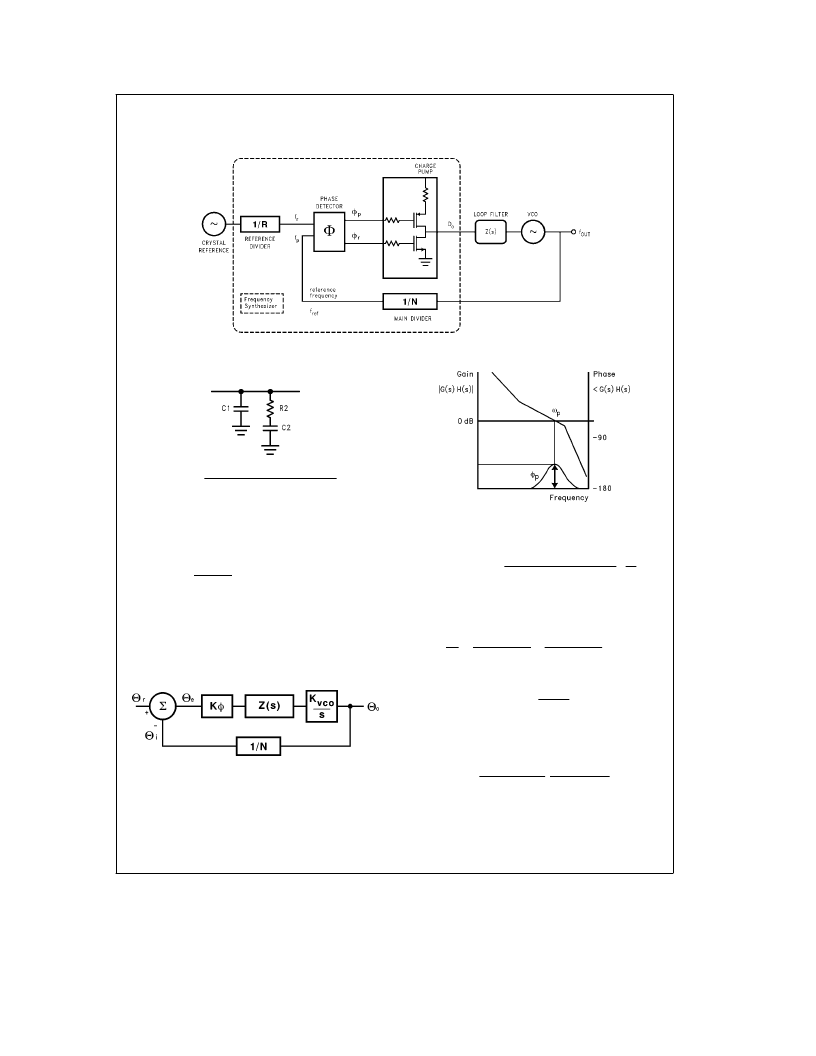

A block diagram of the basic phase locked loop is shown.

TL/W/12458–24

FIGURE 1. Basic Charge Pump Phase Locked Loop

An example of a passive loop filter configuration, including

the transfer function of the loop filter, is shown in Figure 2.

TL/W/12458–25

Z(s)

e

s (C2

#

R2)

a

1

s

2

(C1

#

C2

#

R2)

a

sC1

a

sC2

FIGURE 2. 2nd Order Passive Filter

Define the time constants which determine the pole and

zero frequencies of the filter transfer function by letting

T2

e

R2

#

C2

and

C1

#

C2

C1

a

C2

The PLL linear model control circuit is shown along with the

open loop transfer function in Figure 3. Using the phase

detector and VCO gain constants

[

K

w

and K

VCO

]

and the

loop filter transfer function

[

Z(s)

]

, the open loop Bode plot

can be calculated. The loop bandwidth is shown on the

Bode plot (

0

p) as the point of unity gain. The phase margin

is shown to be the difference between the phase at the unity

gain point and

b

180

§

.

(1a)

T1

e

R2

#

(1b)

TL/W/12458–27

Open Loop Gain

e

i

i

/

i

e

e

H(s) G(s)

e

K

w

Z(s) K

VCO

/Ns

Closed Loop Gain

e

i

o

/

i

i

e

G(s)/

[

1

a

H(s) G(s)

]

TL/W/12458–26

FIGURE 3. Open Loop Transfer Function

Thus we can calculate the 3rd order PLL Open Loop Gain in

terms of frequency

G(s)

#

H(s)

l

s

e

j

#

0

eb

K

w

#

K

VCO

(1

a

j

0

#

T2)

0

2

C1

#

N(1

a

j

0

#

T1)

From equation 2 we can see that the phase term will be

dependent on the single pole and zero such that

w

(

0

)

e

tan

b

1

(

0

#

T2)

b

tan

b

1

(

0

#

T1)

a

180

§

By setting

#

T1

T2

(2)

(3)

d

w

d

0

e

T2

1

a

(

0

#

T2)

2

b

T1

1

a

(

0

#

T1)

2

e

0

(4)

we find the frequency point corresponding to the phase in-

flection point in terms of the filter time constants T1 and T2.

This relationship is given in equation 5.

0

p

e

1/

T2

#

T1

For the loop to be stable the unity gain point must occur

before the phase reaches

b

180 degrees. We therefore

want the phase margin to be at a maximum when the magni-

tude of the open loop gain equals 1. Equation 2 then gives

C1

e

K

w

#

K

VCO

#

T1

(5)

0

p2

#

N

#

T2

ó

(1

a

j

0

p

#

T2)

(1

a

j

0

p

#

T1)

ó

(6)

http://www.national.com

11

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LMX2305TM | PLLatinumTM 550 MHz Frequency Synthesizer for RF Personal Communications |

| LMX2305TMX | PLLatinumTM 550 MHz Frequency Synthesizer for RF Personal Communications |

| LMX2305 | PLLatinum 550 MHz Frequency Synthesizer for RF Personal Communications(PLLatinum技術(shù)用于射頻個(gè)人通訊的550MHZ頻率合成器) |

| LMX2354TM | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2354 | PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LMX2305 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:PLLatinumTM 550 MHz Frequency Synthesizer for RF Personal Communications |

| LMX2305 WAF | 制造商:Texas Instruments 功能描述: |

| LMX2305C WAF | 制造商:Texas Instruments 功能描述: |

| LMX2305TM | 制造商:Rochester Electronics LLC 功能描述: |

| LMX2305TMX | 功能描述:IC FREQ SYNTH DUAL 20-TSSOP RoHS:否 類別:集成電路 (IC) >> 時(shí)鐘/計(jì)時(shí) - 時(shí)鐘發(fā)生器,PLL,頻率合成器 系列:PLLatinum™ 標(biāo)準(zhǔn)包裝:39 系列:- 類型:* PLL:帶旁路 輸入:時(shí)鐘 輸出:時(shí)鐘 電路數(shù):1 比率 - 輸入:輸出:1:10 差分 - 輸入:輸出:是/是 頻率 - 最大:170MHz 除法器/乘法器:無/無 電源電壓:2.375 V ~ 3.465 V 工作溫度:0°C ~ 70°C 安裝類型:* 封裝/外殼:* 供應(yīng)商設(shè)備封裝:* 包裝:* |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。