- 您現在的位置:買賣IC網 > PDF目錄361044 > LMX2430 (National Semiconductor Corporation) PLLatinum Dual High Frequency Synthesizer for RF Personal Communications PDF資料下載

參數資料

| 型號: | LMX2430 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | PLLatinum Dual High Frequency Synthesizer for RF Personal Communications |

| 中文描述: | PLLatinum雙高頻率合成射頻個人通信 |

| 文件頁數: | 30/49頁 |

| 文件大小: | 943K |

| 代理商: | LMX2430 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

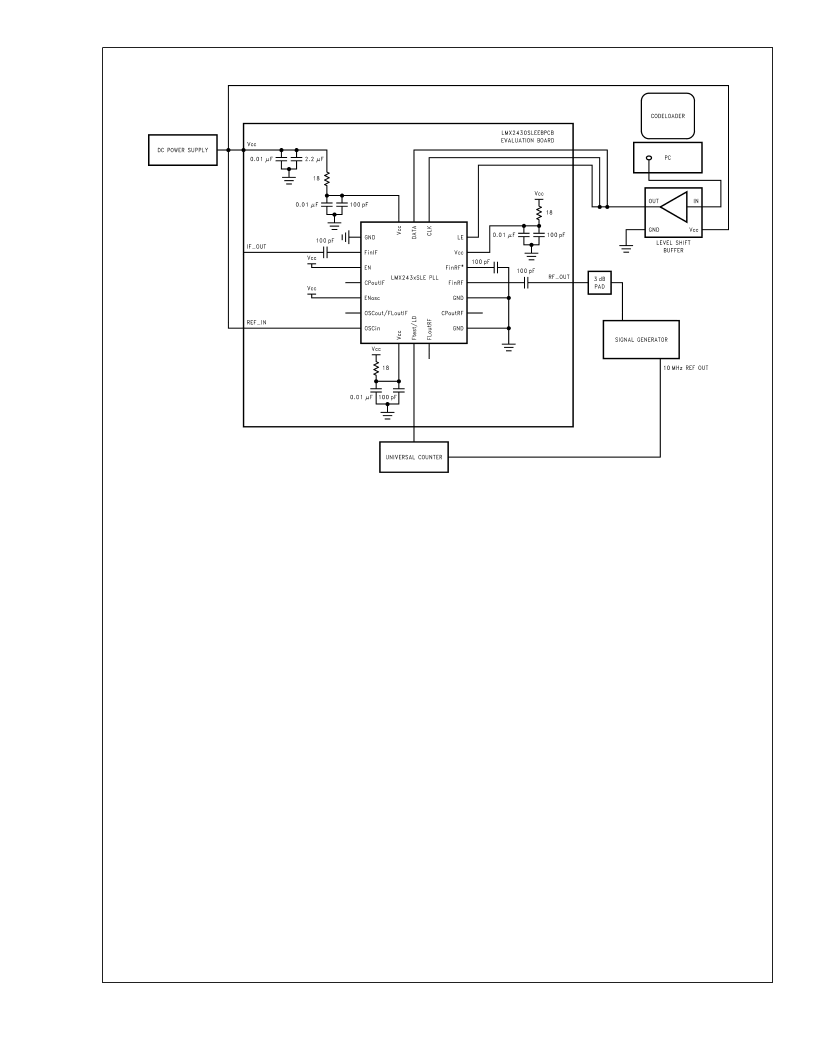

LMX243x FinRF Sensitivity Test Setup

20053589

The block diagram above illustrates the setup required to

measure the LMX243x device’s RF input sensitivity level.

The same setup is used for the LMX2430TM Evaluation

Board. The purpose of this test is to measure the acceptable

signal level to the FinRF input of the PLL chip. Outside the

acceptable signal range, the feedback divider begins to di-

vide incorrectly and miscount the frequency. The FinIF sen-

sitivity is evaluated in the same way.

The setup uses an open loop configuration. A power supply

is connected to Vcc. The IF PLL is powered down (IF_PD bit

= 1). By means of a signal generator, an RF signal is applied

to the FinRF pin. The 3 dB pad provides a 50

match

between the PLL and the signal generator. The EN, ENosc,

and OSCin pins are all tied to Vcc. The N value is typically

set to 10000 in CodeLoader, i.e. RF_B word = 156 and

RF_A word = 16 for RF_P bit = 0 (LMX2434) or RF_P bit =

1 (LMX2430 and LMX2433). The feedback divider output is

routed to the Ftest/LD pin by selecting the RF_N/2 Fre-

quency word (MUX[3:0] word = 15) in CodeLoader. A Uni-

versal Counter is connected to the Ftest/LD pin and used to

monitor the output frequency of the feedback divider. The

expected frequency should be the signal generator fre-

quency divided by twice the corresponding counter value,

i.e. 20000. The factor of two comes in because the LMX43x

device has an internal /2 circuit which is used to provide a

50% duty cycle.

Sensitivity is typically measured over frequency, supply volt-

age and temperature. In order to perform the measurement,

the temperature, frequency, and supply voltage is set to a

fixed value and the power level of the signal at FinRF is

varied. Sensitivity is reached when the frequency error of the

divided RF input is greater than or equal to 1 Hz. The power

attenuation from the cable and the 3 dB pad must be ac-

counted for. The feedback divider will actually miscount if too

much or too little power is applied to the FinRF input. There-

fore, the allowed input power level will be bounded by the

upper and lower sensitivity limits. In a typical application, if

the power level to the FinRF input approaches the sensitivity

limits, this can introduce spurs or cause degradation to the

phase noise. When the power level gets even closer to these

limits, or exceeds it, then the RF PLL loses lock.

L

www.national.com

30

相關PDF資料 |

PDF描述 |

|---|---|

| LMX2433TM | PLLatinum Dual High Frequency Synthesizer for RF Personal Communications |

| LMX2433TMX | PLLatinum Dual High Frequency Synthesizer for RF Personal Communications |

| LMX2434 | PLLatinum Dual High Frequency Synthesizer for RF Personal Communications |

| LMX2434TM | PLLatinum Dual High Frequency Synthesizer for RF Personal Communications |

| LMX2434TMX | PLLatinum Dual High Frequency Synthesizer for RF Personal Communications |

相關代理商/技術參數 |

參數描述 |

|---|---|

| LMX2430EVAL | 功能描述:EVALUATION BOARD FOR LMX2430 RoHS:否 類別:編程器,開發系統 >> 評估演示板和套件 系列:PLLatinum™ 標準包裝:1 系列:PCI Express® (PCIe) 主要目的:接口,收發器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要屬性:- 次要屬性:- 已供物品:板 |

| LMX2430EVAL/NOPB | 功能描述:時鐘和定時器開發工具 LMX2430 EVAL BOARD RoHS:否 制造商:Texas Instruments 產品:Evaluation Modules 類型:Clock Conditioners 工具用于評估:LMK04100B 頻率:122.8 MHz 工作電源電壓:3.3 V |

| LMX2430SLEX | 制造商:Texas Instruments 功能描述:3GHZ HI FREQ DUAL PLL SMD 2430 |

| LMX2430SLEX/NOPB | 功能描述:鎖相環 - PLL RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| LMX2430SLEXNOPB | 制造商:National Semiconductor 功能描述:PLL Frequency Synthesizer Dual 100MHz to 3000MHz 20-Pin LAM UCSP T/R |

發布緊急采購,3分鐘左右您將得到回復。