- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371044 > MC68341 (Motorola, Inc.) Integrated Processor Users Manual PDF資料下載

參數(shù)資料

| 型號: | MC68341 |

| 廠商: | Motorola, Inc. |

| 英文描述: | Integrated Processor Users Manual |

| 中文描述: | 綜合處理器用戶手冊 |

| 文件頁數(shù): | 12/21頁 |

| 文件大小: | 134K |

| 代理商: | MC68341 |

MOTOROLA

MC68341 USER’S MANUAL ADDENDUM

11

38. Additional Notes on DMA Features

In the feature set listed on page 6-1, bullet six is “Operand Packing and Unpacking for Dual-Address Trans-

fers”. This packing is for transfers between different port sizes selected in the DMA channel control register,

e.g. Byte <> Word transfers. The DMA controller does not do packing for byte > byte transfers, eliminating the

problem of residual bytes left in the controller when a channel is stopped after an odd byte transfer count.

39. Additional Note on Internal Request Generation

Add to the Internal Request Generation section on page 6-5: For internal request operation, DACKx and DON-

Ex are not active as outputs during transfers. DONEx is valid as an input though and will terminate channel

operation if asserted - pull up if not used.

40. Additional Note on DMA Transfer Latency from DREQ

Add to the External Request Generation section beginning 6-5: DREQx assertions require two clocks for input

synchronization and IMB bus arbitration activity before the resulting DMA bus cycle can start. A DREQx as-

sertion will preempt the next CPU bus cycle if it is recognized two or more clocks before the end of the current

bus cycle, unless the current cycle is not the last cycle of an operand transfer, or is the read of an RMC cycle.

Operand transfers and RMC read/write sequences are indivisible to guarantee data coherency - the bus can-

not be arbitrated from the CPU until the complete operand transfer completes, even if operand and memory

sizing results in multiple bus cycles.

For a DREQx assertion during an idle bus period, bus state S0 of the DMA bus cycle starts 2.5 clocks after the

clock falling edge which DREQx is recognized on. The maximum latency from the clock falling edge that

DREQx is recognized on to the falling edge that AS for the DMA cycle asserts from is shown in the following

table for various memory speeds.

41. Additional Note on Burst Transfer DREQx Negation and Overhead

On page 6-5, replace the 2nd paragraph of 6.3.2.1 External Burst Mode with the following: DREQx must be

negated one clock before the end of the last DMA bus cycle of a burst to prevent another DMA transfer from

being generated. Also, DREQx must be negated two clocks before the end of the last DMA bus cycle to prevent

an idle clock between that transfer and the following CPU access.

42. Additional Note on Cycle steal DMA arbitration overhead

Add to the External Cycle Steal Mode description on page 6-6: In general, DMA arbitration occurs transpar-

ently. However, for some 2-clock accesses using cycle steal an idle clock can follow the DMA transfer due to

incomplete overlap of the DMA transfer with internal IMB arbitration. Specifically, an idle clock can follow 1)

single address 2-clock transfers and 2) dual address transfers from memory to 2-clock devices. Arbitration is

completely overlapped for all other cases.

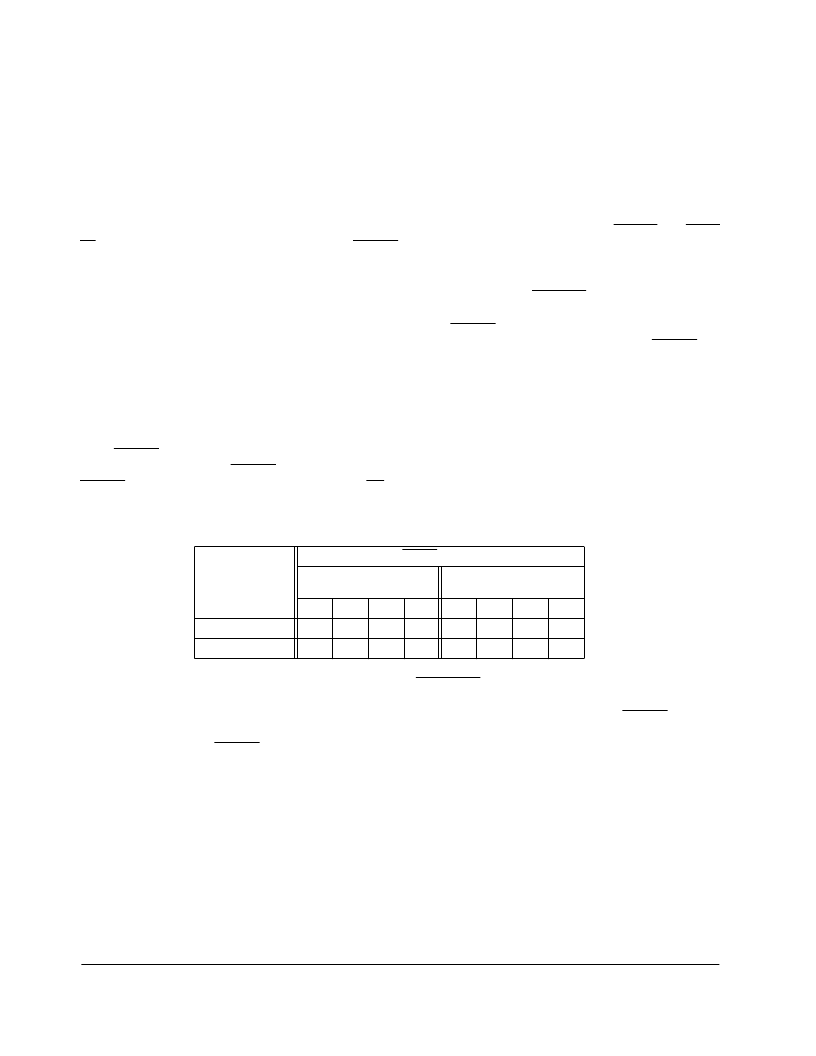

DREQ Latency (Clocks) vs. Bus Width and Access Times

Maximum DREQ Latency (Clocks)

16-Bit Bus

Clocks/Bus Cycle

3

4

5

9

11

13

10

12

14

16

Access Type

8-Bit Bus

Clocks/Bus Cycle

3

11

15

10

12

2

7

2

4

19

14

5

23

16

Longword

RMC (TAS)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC6835 | 8-BIT MPUS, 8-BIT MCUS, 8-BIT PERIPHERALS |

| MC6843 | 8-BIT MPUS, 8-BIT MCUS, 8-BIT PERIPHERALS |

| MC6844 | 8-BIT MPUS, 8-BIT MCUS, 8-BIT PERIPHERALS |

| MC6846 | 8-BIT MPUS, 8-BIT MCUS, 8-BIT PERIPHERALS |

| MC6852 | 8-BIT MPUS, 8-BIT MCUS, 8-BIT PERIPHERALS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68341FT16 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Integrated Processor Users Manual |

| MC68341FT16V | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Integrated Processor Users Manual |

| MC68341FT25 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Integrated Processor Users Manual |

| MC68341UMAD | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Integrated Processor Users Manual |

| MC68349 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HIGH PERFORMANCE INTEGRATED PROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。