- 您現在的位置:買賣IC網 > PDF目錄361089 > NCN6000 (ON SEMICONDUCTOR) Compact Smart Card Interface IC(智能卡接口集成電路) PDF資料下載

參數資料

| 型號: | NCN6000 |

| 廠商: | ON SEMICONDUCTOR |

| 英文描述: | Compact Smart Card Interface IC(智能卡接口集成電路) |

| 中文描述: | 緊湊型智能卡接口IC(智能卡接口集成電路) |

| 文件頁數: | 11/36頁 |

| 文件大小: | 358K |

| 代理商: | NCN6000 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

NCN6000

http://onsemi.com

11

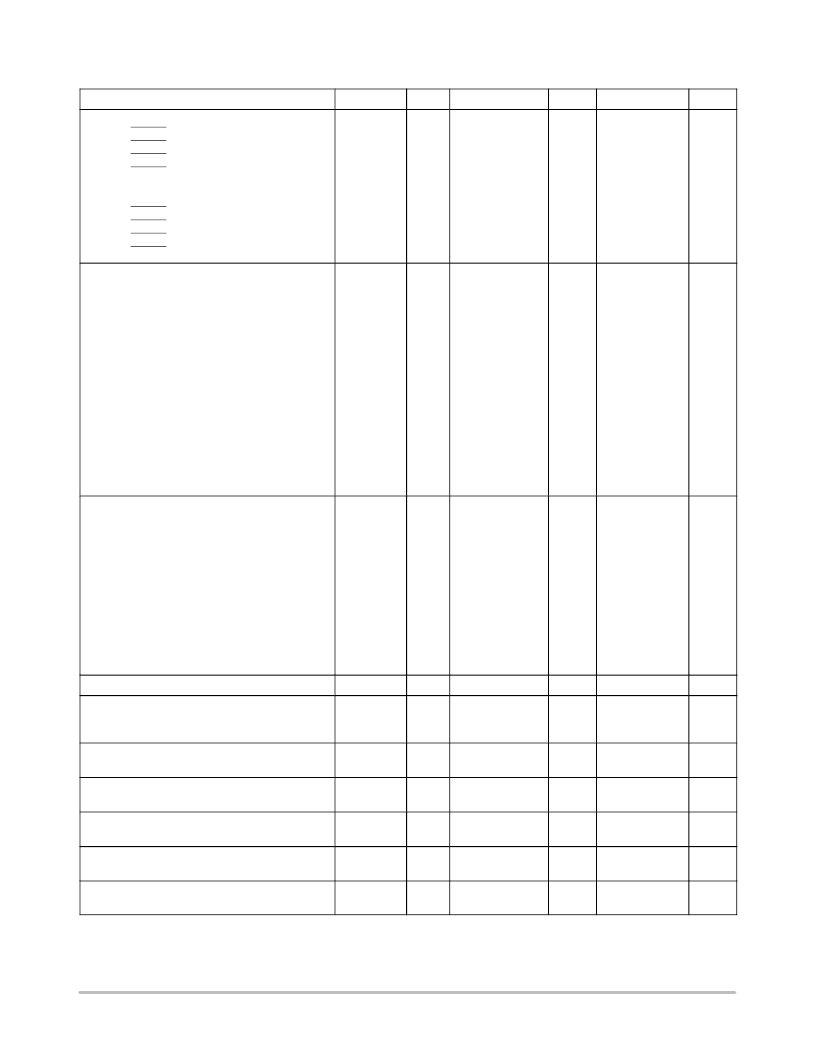

SMART CARD SECTION

(25

°

C to +85

°

C ambient temperature, unless otherwise noted.)

Rating

Symbol

Pin

Min

Typ

Max

Unit

CRD_RST @ CRD_VCC = +5.0 V

Output RESET V

OH

@ Icrd_rst = 20 A

Output RESET V

OL

@ Icrd_rst = 200 A

Output RESET Rise Time @ Cout = 30 pF

Output RESET Fall Time @ Cout = 30 pF

CRD_RST @ Vcc = +3.0 V

Output RESET V

OH

@ Icrd_rst = 20 A

Output RESET V

OL

@ Icrd_rst = 200 A

Output RESET Rise Time @ Cout = 30 pF

Output RESET Fall Time @ Cout = 30 pF

V

OH

V

OL

t

R

t

F

V

OH

V

OL

t

R

t

F

12

CRD_VCC 0.9

0

CRD_VCC 0.9

0

CRD_VCC

0.4

100

100

CRD_VCC

0.4

100

100

V

V

ns

ns

V

V

ns

ns

CRD_CLK @ CRD_VCC = +3.0 V or +5.0 V

CRD_VCC = +5.0 V

Output Frequency (See Note 8)

Output Duty Cycle @ DC Fin = 50%

Output CRD_CLK Rise Time @ Cout = 30 pF

Output CRD_CLK Fall Time @ Cout = 30 pF

Output V

OH

@ Icrd_clk = 20 A

Output V

OL

@ Icrd_clk = 100 A

1%

CRD_VCC = +3.0 V

Output Frequency (See Note 8)

Output Duty Cycle @ DC Fin = 50%

Output CRD_CLK Rise Time @ Cout = 30 pF

Output CRD_CLK Fall Time @ Cout = 30 pF

Output V

OH

@ Icrd_clk = 20 A @ Cout = 30 pF

Output V

OL

@ Icrd_clk = 100 A @ Cout = 30 pF

1%

F

CRDCLK

F

CRDDC

t

R

t

F

V

OH

V

OL

F

CRDCLK

F

CRDDC

t

R

t

F

V

OH

V

OL

13

45

3.15

0

40

1.85

0

5.0

55

18

18

CRD_VCC

+0.5

5.0

60

18

18

CRD_VCC

0.7

MHz

%

ns

ns

V

V

MHz

%

ns

ns

V

V

CRD_I/O @ CRD_VCC = +5.0 V

CRD_I/O Data Transfer Frequency

CRD_I/O Rise Time @ Cout = 30 pF

CRD_I/O Fall Time @ Cout = 30 pF

Output V

OH

@ Icrd_i/o = 20 A

Output V

OL

@ Icrd_i/o = 500 A, V

IL

= 0 V

CRD_I/O @ CRD_VCC = +3.0 V

CRD_I/O Data Transfer Frequency

CRD_I/O Rise Time @ Cout = 30 pF

CRD_I/O Fall Time @ Cout = 30 pF

Output V

OH

@ Icrd_i/o = 20 A

Output V

OL

@ Icrd_i/o = 500 A, V

IL

= 0 V

F

IO

T

RIO

T

FIO

V

OH

V

OL

F

IO

T

RIO

T

FIO

V

OH

V

OL

14

CRD_VCC 0.9

0

CRD_VCC 0.9

0

315

315

0.8

0.8

CRD_VCC

0.4

0.8

0.8

CRD_VCC

0.4

kHz

s

s

V

V

kHz

s

s

V

V

CRD_IO Pull Up Resistor @ PWR_ON = H

R

CRDPU

14

14

20

26

k

Card Detection Debouncing Delay:

Card Insertion

Card Extraction

T

CRDIN

T

CRDOFF

11

50

50

150

150

s

s

Card Insertion or Extraction Positive Going Input

High Voltage

V

IHDET

11

0.70 * Vbat

Vbat

V

Card Insertion or Extraction Negative Going Input

Low Voltage

V

ILDET

11

0

0.30 * Vbat

V

Card Detection Bias Pull Up Current @

Vbat = 5.0 V

I

DET

11

10

A

Output Peak Max Current Under Card Static

Operation Mode @ Vcc = 3.0 V or Vcc = 5.0 V

Icrd_iorst

12, 14

15

mA

Output Peak Max Current Under Card Static

Operation Mode @ Vcc = 3.0 V or Vcc = 5.0 V

Icrd_clk

13

70

mA

8. The CRD_CLK clock can operate up to 20 MHz, but the rise and fall time are not guaranteed to be fully within the ISO7816 specification over

the temperature range. Typically, tr and tf are 12 ns @ CRD_CLK = 10 MHz.

相關PDF資料 |

PDF描述 |

|---|---|

| NCN6001DTBR2 | Compact Smart Card Interface IC |

| NCN6001 | Compact Smart Card Interface IC |

| NCN6004AFTBR2 | Dual SAM/SIM Interface Integrated Circuit |

| NCN6004A | Dual SAM/SIM Interface Integrated Circuit |

| NCN6010DTBR2 | SIM Card Supply and Level Shifter |

相關代理商/技術參數 |

參數描述 |

|---|---|

| NCN6000/D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Compact Smart Card Interface IC |

| NCN6000DTB | 功能描述:輸入/輸出控制器接口集成電路 2.7V POS/ATM Smart RoHS:否 制造商:Silicon Labs 產品: 輸入/輸出端數量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| NCN6000DTBG | 功能描述:輸入/輸出控制器接口集成電路 2.7V POS/ATM Smart Card Interface RoHS:否 制造商:Silicon Labs 產品: 輸入/輸出端數量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| NCN6000DTBR2 | 功能描述:輸入/輸出控制器接口集成電路 2.7V POS/ATM Smart RoHS:否 制造商:Silicon Labs 產品: 輸入/輸出端數量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| NCN6000DTBR2G | 功能描述:輸入/輸出控制器接口集成電路 2.7V POS/ATM Smart Card Interface RoHS:否 制造商:Silicon Labs 產品: 輸入/輸出端數量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

發布緊急采購,3分鐘左右您將得到回復。