- 您現在的位置:買賣IC網 > PDF目錄98254 > TLV320AIC33IRGZTG4 (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQCC48 PDF資料下載

參數資料

| 型號: | TLV320AIC33IRGZTG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| 封裝: | 7 X 7 MM, GREEN, PLASTIC, VQFN-48 |

| 文件頁數: | 24/93頁 |

| 文件大小: | 1427K |

| 代理商: | TLV320AIC33IRGZTG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁

STEREO AUDIO ADC

SLAS480B – JANUARY 2006 – REVISED DECEMBER 2008 ........................................................................................................................................... www.ti.com

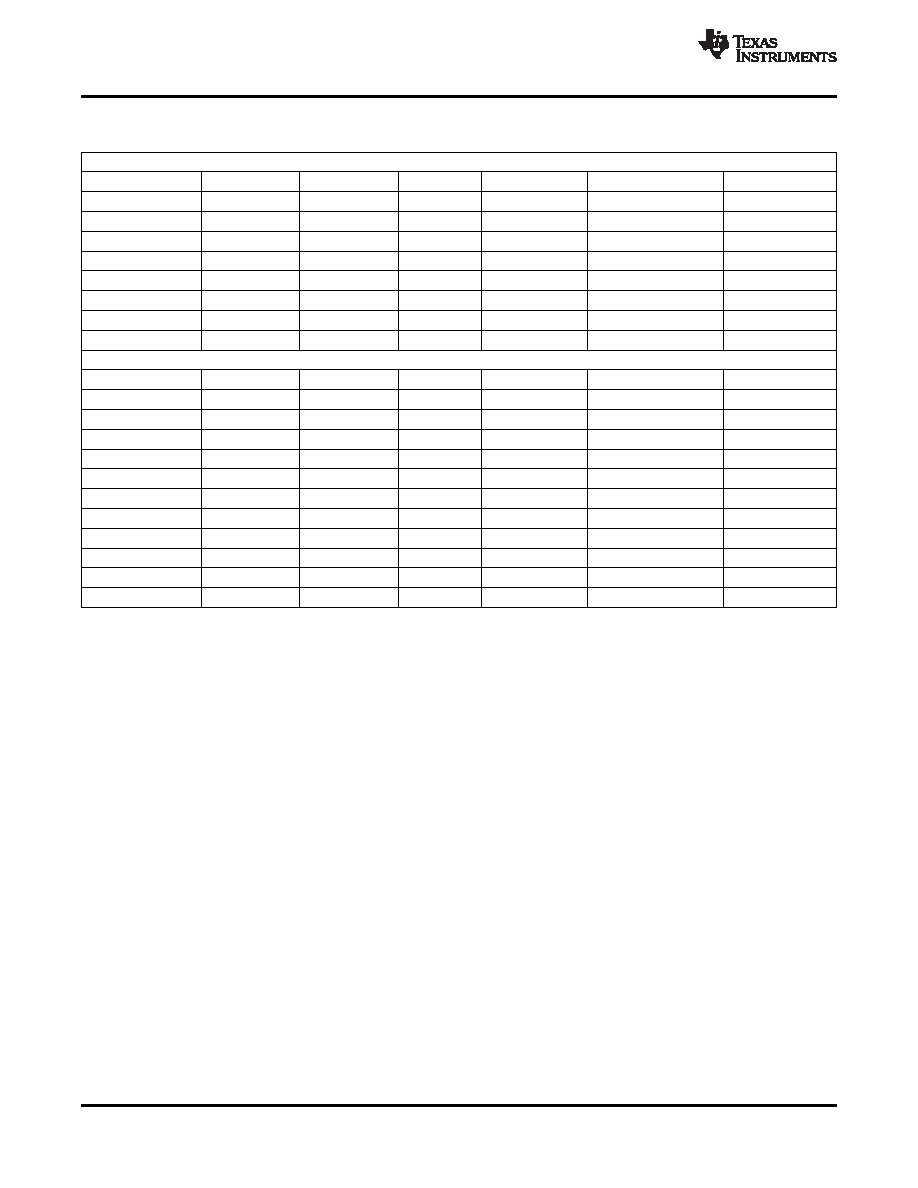

The table below lists several example cases of typical MCLK rates and how to program the PLL to achieve

Fsref = 44.1 kHz or 48 kHz.

Fsref = 44.1 kHz

MCLK (MHz)

P

R

J

D

ACHIEVED FSREF

% ERROR

2.8224

1

32

0

44100.00

0.0000

5.6448

1

16

0

44100.00

0.0000

12.0

1

7

5264

44100.00

0.0000

13.0

1

6

9474

44099.71

0.0007

16.0

1

5

6448

44100.00

0.0000

19.2

1

4

7040

44100.00

0.0000

19.68

1

4

5893

44100.30

–0.0007

48.0

4

1

7

5264

44100.00

0.0000

Fsref = 48 kHz

MCLK (MHz)

P

R

J

D

ACHIEVED FSREF

% ERROR

2.048

1

48

0

48000.00

0.0000

3.072

1

32

0

48000.00

0.0000

4.096

1

24

0

48000.00

0.0000

6.144

1

16

0

48000.00

0.0000

8.192

1

12

0

48000.00

0.0000

12.0

1

8

1920

48000.00

0.0000

13.0

1

7

5618

47999.71

0.0006

16.0

1

6

1440

48000.00

0.0000

19.2

1

5

1200

48000.00

0.0000

19.68

1

4

9951

47999.79

0.0004

48.0

4

1

8

1920

48000.00

0.0000

The AIC33 can also output a separate clock on the GPIO1 pin. If the PLL is being used for the audio data

converter clock, the M and N settings can be used to provide a divided version of the PLL output. If the PLL is

not being used for the audio data converter clock, the PLL can still be enabled to provide a completely

independent clock output on GPIO1. The formula for the GPIO1 clock output when PLL is enabled and

CLKMUX_OUT is 0 is:

GPIO1 = (PLLCLK_IN× 2 × K × R) / (M × N × P)

When CLKMUX_OUT is 1, regardless of whether PLL is enabled or disabled, the input to the clock output divider

can be selected as MCLK, BCLK, or GPIO2. Is this case, the formula for the GPIO1 clock is:

GPIO1 = (CLKDIV_IN × 2) / (M × N), where

M = 1, 2, 4, 8

N = 2, 3, …, 17

CLKDIV_IN can be BCLK, MCLK, or GPIO2, selected by page 0, register 102, bits D7-D6

The TLV320AIC33 includes a stereo audio ADC, which uses a delta-sigma modulator with 128-times

oversampling in single-rate mode, followed by a digital decimation filter. The ADC supports sampling rates from 8

kHz to 48 kHz in single-rate mode, and up to 96 kHz in dual-rate mode. Whenever the ADC or DAC is in

operation, the device requires an audio master clock be provided and appropriate audio clock generation be

setup within the part.

In order to provide optimal system power dissipation, the stereo ADC can be powered one channel at a time, to

support the case where only mono record capability is required. In addition, both channels can be fully powered

or entirely powered down.

30

Copyright 2006–2008, Texas Instruments Incorporated

Product Folder Link(s): TLV320AIC33

相關PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC33IRGZ | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| TLV320AIC36IZQER | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC36IZQE | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320DAC23IPW | SERIAL INPUT LOADING, 32-BIT DAC, PDSO28 |

| TLV320DAC23IGQER | SERIAL INPUT LOADING, 32-BIT DAC, PBGA80 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV320AIC33IZQE | 功能描述:接口—CODEC Lo-Pwr Stereo Codec w/6 Inp 7 Otp RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC33IZQE | 制造商:Texas Instruments 功能描述:AUDIO CODEC IC ((NW)) |

| TLV320AIC33IZQER | 功能描述:接口—CODEC Lo-Pwr Stereo Codec w/6 Inp 7 Otp RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC33NIZQE | 制造商:Texas Instruments 功能描述: |

| TLV320AIC33NIZQER | 制造商:Texas Instruments 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。