- 您現在的位置:買賣IC網 > PDF目錄365968 > TSB12LV26PZ (Texas Instruments, Inc.) OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER PDF資料下載

參數資料

| 型號: | TSB12LV26PZ |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | OHCI-Lynx PCI-BASED IEEE 1394 HOST CONTROLLER |

| 中文描述: | OHCI的山貓基于PCI的1394主控制器 |

| 文件頁數: | 91/106頁 |

| 文件大小: | 605K |

| 代理商: | TSB12LV26PZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁當前第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁

7

–

13

7.4

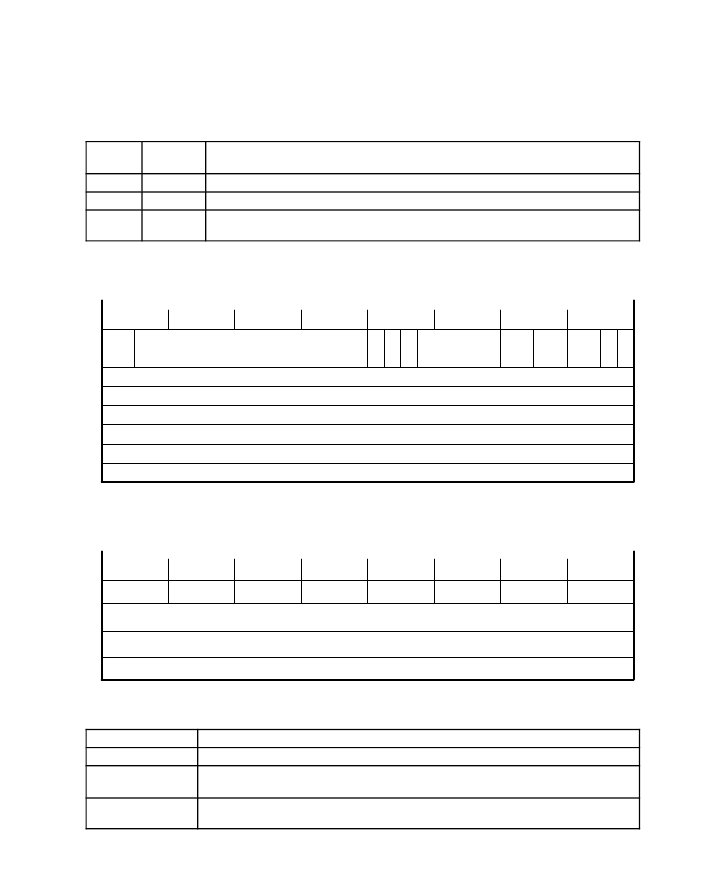

Based on the settings of the RXSID and FULLSID bits in the control register @08h, the self-ID packets can

be either ignored or received into the GRF. Refer to Table 7

–

13.

Receive Self-ID Packet

Table 7

–

13. GRF Receive Self-ID Setup Using Control Register Bits (RXSID and FULLSID)

RXSID

(bit 1)

FULLSID

(bit 2)

OPERATION

0

X

Self-ID packets are not received by the link.

1

0

Only the data quadlet (first quadlet) of the self-ID packets are received into the GRF.

1

1

soth the data quadlet (first quadlet) and the logical inverse quadlet (second quadlet) of all

Self-ID packets are received into the GRF.

Figures 7

–

17 and 7

–

18 show the format of a received self-ID packet. For completeness, the figures assume

the cable Phy on the bus implements the maximum number of ports allowed by the P1394a specification.

Both figures show one received self-ID packet. The contents are described in Table 7

–

14.

3

2

1

0

7

6

5

4

11

10

9

8

15

14

13

12

19

18

20 21

31

30

29

28

27

26

25

24

23

22

0

0

numofQuadlets

0

0

spd

0

0

ackCode

Self-ID Data Quadlet #0

0

0

0

17

16

L

L

Logical Inverse of the Self-ID Quadlet #0

Self-ID Data Quadlet #1

Logical Inverse of the Self-ID Quadlet #1

Self-ID Data Quadlet #2

Logical Inverse of theSelf-ID Quadlet #2

Figure 7

–

17. Receive Self-ID Packet Format (RXSID=1, FULLSID=1)

Figure 7

–

18 shows the format of the received self-ID packet when the FULLSID is cleared. In this case, only

the first quadlet of each self-ID packet is received in the GRF.

3

2

1

0

7

6

5

4

11

10

9

8

15

14

13

12

19

18

20 21

31

30

29

28

27

26

25

24

23

22

0

0

0

0

1

1

Self-ID Data Quadlet #0

0

0

0

17

16

Self-ID Data Quadlet #1

Self-ID Data Quadlet #2

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

Figure 7

–

18. Receive Self-ID Packet Format (RXSID=1, FULLSID=0)

Table 7

–

14. Receive Self-ID Function

FIELD NAME

DESCRIPTION

Self-ID Data Quadlet

First 32-bits of the first self-ID packet

Logical Inverse of the

Self-ID Quadlet

Second 32-bits of the first self-ID packet

ACK

When the ACK field is set (0001), the data in the Self-ID packet is correct. When ACK is

≠

0001,

the data in the self-ID packet is incorrect.

相關PDF資料 |

PDF描述 |

|---|---|

| TSB14AA1 | FPGA (Field-Programmable Gate Array) |

| TSB14AA1I | FPGA (Field-Programmable Gate Array) |

| TSB14AA1T | FPGA (Field-Programmable Gate Array) |

| TSB14C01MHV | IC APEX 20KE FPGA 160K 484-FBGA |

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TSB12LV26PZT | 功能描述:1394 接口集成電路 OHCI-Lynx PCI-Based Host Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV26PZTG4 | 功能描述:1394 接口集成電路 OHCI-Lynx PCI-Based IEEE1394 Host Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV26TPZEP | 功能描述:1394 接口集成電路 Mil Enh OHCI-Lynx IEEE 1394 Host Cntlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV31 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB12LV31PZ | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 General-Purpose Link-Layer Controller |

發布緊急采購,3分鐘左右您將得到回復。