- 您現在的位置:買賣IC網 > PDF目錄36340 > 935269576557 (NXP SEMICONDUCTORS) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF資料下載

參數資料

| 型號: | 935269576557 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | 14 X 14 MM, 1 MM HEIGHT, HEAT SINK, PLASTIC, SOT-638-1, TQFP-100 |

| 文件頁數: | 37/84頁 |

| 文件大小: | 1054K |

| 代理商: | 935269576557 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

Koninklijke Philips Electronics N.V. Copyright 2001. All rights reserved.

9397 750 08865

42 of 84

Rev. 02 — 8 October 2001

Product data

PNX8510/11

Philips Semiconductors

Analog Companion Chip

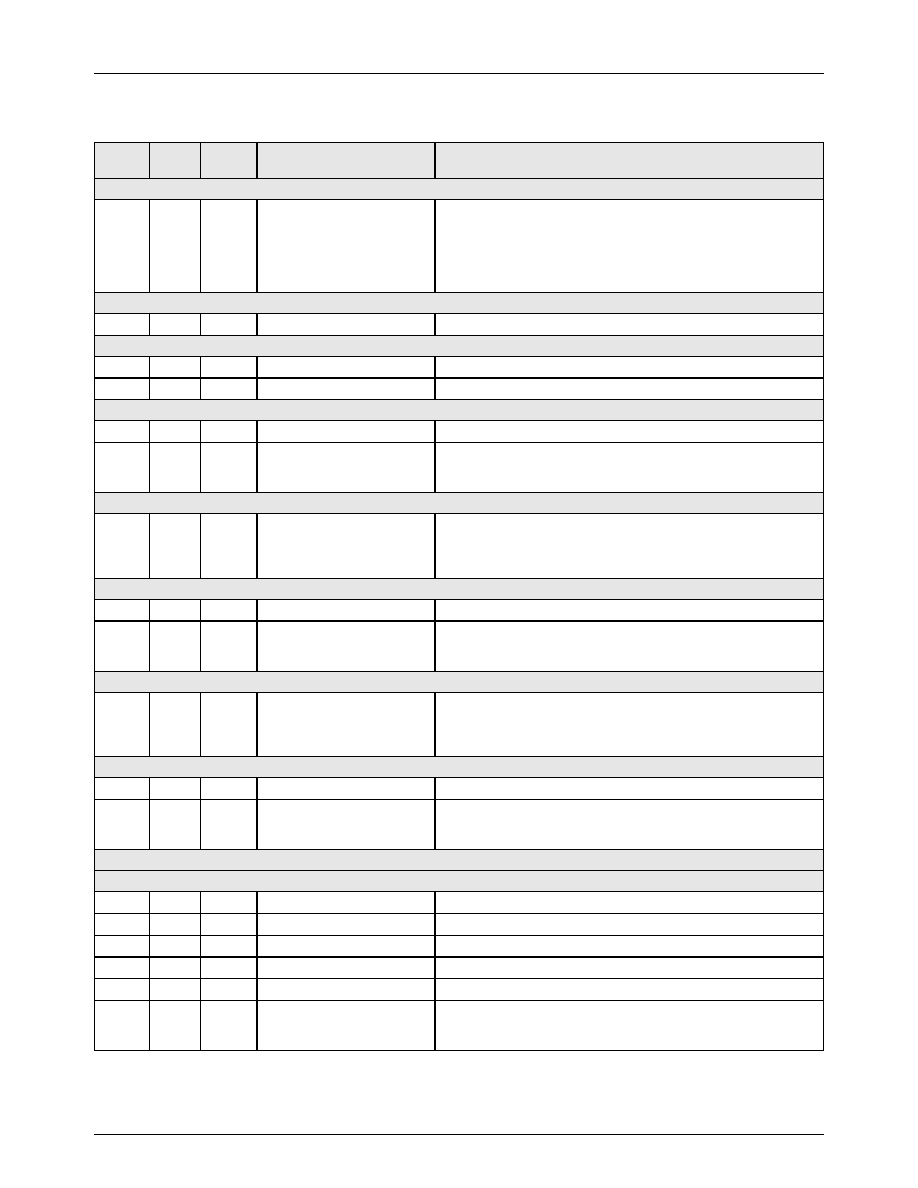

Offset 0x7F

DTTXL2

7:0

R/W

0x00

DTTXL

Individual lines in both fields (PAL counting) can be disabled for

insertion of teletext by the respective bits.

Disabled line = LINExx(50Hz field rate)

Bit 7 = Line 20; Bit 0 = Line 13

The mask is only effective if the lines are enabled via TTXOVS/

TTXOVE and TTXEVS/TTXEVE.

Offset 0x80

LCNT_ARRAY_LINE - Not present in secondary video channel.

7:0

R/W

-

LCNT_ARRAY_LINE

Line count array programming data lower 8 bits

Offset 0x81

LCNT_ARRAY_LINE - Not present in secondary video channel.

7:6

-

Unused

5:0

R/W

-

LCNT_ARRAY_LINE

Line count array programming data upper 6 bit

Offset 0x82

LCNT_ARRAY_ADR - Not present in secondary video channel.

7:4

-

Unused

3:0

R/W

-

LCNT_ARRAY_ADR

Line count array programming address

Writing to this address initiates the transfer of the data previously

written into locations 80 and 81 into an internal register array.

Offset 0x83—0x85

LTYPE_ARRAY_LINE - Not present in secondary video channel.

7:0

R/W

-

LTYPE_ARRAY_LINE

0x83 -> LSBs

0x85 -> MSBs

Line type array programming data

2:0 = first index

...

23:21 = last index

Offset 0x86

LTYPE_ARRAY_ADR - Not present in secondary video channel.

7:4

-

Unused

3:0

R/W

-

LTYPE_ARRAY_ADR

Line type array programming address

Writing to this address initiates the transfer of the data previously

written into locations 83 through 85 into an internal register array.

Offset 0x87—0x8D

LPATT_ARRAY_LINE - Not present in secondary video channel.

7:0

R/W

-

LPATT_ARRAY_LINE

0x87 -> LSBs

0x8D -> MSBs

Line pattern array programming data

13:4 = first duration 3:0 = first index

...

55:46 = last duration 45:42 last index

Offset 0x8E

LPATT_ARRAY_ADR - Not present in secondary video channel.

7:3

-

Unused

2:0

R/W

-

LTYPE_ARRAY_ADR

Line pattern array programming address

Writing to this address initiates the transfer of the data previously

written into locations 87 through 8D into an internal register array.

Offset 0x8F

must be initialized to zero.

Offset 0x90—0x94

GPIO5-GPIO1 (0x90=GPIO1, ..., 0x94=GPIO5) Not present in secondary video channel.

7

R/W

0

GPIO_IN_EN4

GPIO input enable 4

6

R/W

0

GPIO_IN_EN3

GPIO input enable 3

5

R/W

0

GPIO_IN_EN2

GPIO input enable 2

4

R/W

0

GPIO_IN_EN1

GPIO input enable 1

3

R/W

1

OEN

Output enable

2

R/W

0

STATUS

Write to register sets the GPIO pin if output select is set to 2’b11.

Read to register returns the status of the gpio pin if GPIO_IN_EN4

is set, otherwise it returns 0.

Bits

Read/

Write

Reset

Value

Name

(Field or Function)

Description

相關PDF資料 |

PDF描述 |

|---|---|

| 935269580557 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 935270418112 | 8-CHANNEL, SGL ENDED MULTIPLEXER, PDSO16 |

| 935270418118 | 8-CHANNEL, SGL ENDED MULTIPLEXER, PDSO16 |

| 933669740652 | 8-CHANNEL, SGL ENDED MULTIPLEXER, PDIP16 |

| 933670370112 | 8-CHANNEL, SGL ENDED MULTIPLEXER, PDIP16 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

| 935270713557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC CHP |

| 935270792551 | 制造商:NXP Semiconductors 功能描述:IC BUFF DVR TRI-ST 16BIT 56VFBGA |

| 935270792557 | 制造商:NXP Semiconductors 功能描述:IC BUFF DVR TRI-ST 16BIT 56VFBGA |

| 935270793551 | 制造商:NXP Semiconductors 功能描述:IC BUS TRCVR 3-ST 16BIT 56VFBGA |

發布緊急采購,3分鐘左右您將得到回復。