- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373913 > AD7703CR (ANALOG DEVICES INC) ECONOLINE: REC2.2-S_DRW(Z)/H* - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- 4.5-9V, 9-18V, 18-36V, 36-72V Wide Input Range 2 : 1- UL94V-0 Package Material- Continuous Short Circiut Protection- Cost Effective- 100% Burned In- Efficiency to 84% PDF資料下載

參數(shù)資料

| 型號(hào): | AD7703CR |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | ECONOLINE: REC2.2-S_DRW(Z)/H* - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- 4.5-9V, 9-18V, 18-36V, 36-72V Wide Input Range 2 : 1- UL94V-0 Package Material- Continuous Short Circiut Protection- Cost Effective- 100% Burned In- Efficiency to 84% |

| 中文描述: | 1-CH 20-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO20 |

| 封裝: | MS-013AC, SOIC-20 |

| 文件頁(yè)數(shù): | 11/16頁(yè) |

| 文件大小: | 251K |

| 代理商: | AD7703CR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

AD7703

REV. D

–11–

T able V. AD7703 Output Coding

I

NPUT VOLT AGE , UNIPOLAR MODE INPUT VOLT AGE , BIPOLAR MODE

System Cal

Self Cal

Output Codes

Self-Cal

System Cal

>(

S

GAIN

–1.5 LSB)

>

(V

REF

– 1.5 LSB)

FFFFF

>

(V

REF

–1.5 LSB)

>

(S

GAIN

– 1.5 LSB)

S

GAIN

– 1.5 LSB

V

REF

– 1.5 LSB

FFFFF

FFFFE

V

REF

– 1.5 LSB

S

GAIN

– 1.5 LSB

(S

GAIN

– S

OFF

)/2 – 0.5 LSB

(V

REF

– V

AGND

)/2 – 0.5 LSB

80000

7FFFF

V

AGND

– 0.5 LSB

S

OFF

– 0.5 LSB

S

OFF

+ 0.5 LSB

V

AGND

+ 0.5 LSB

00001

00000

–V

REF

+ 0.5 LSB

–S

GAIN

+ 2 S

OFF

+ 0.5 LSB

<

(S

OFF

+ 0.5 LSB)

<

(V

AGND

+ 0.5 LSB)

00000

<

(–V

REF

+ 0.5 LSB)

<(–S

GAIN

+2 S

OFF

+ 0.5 LSB)

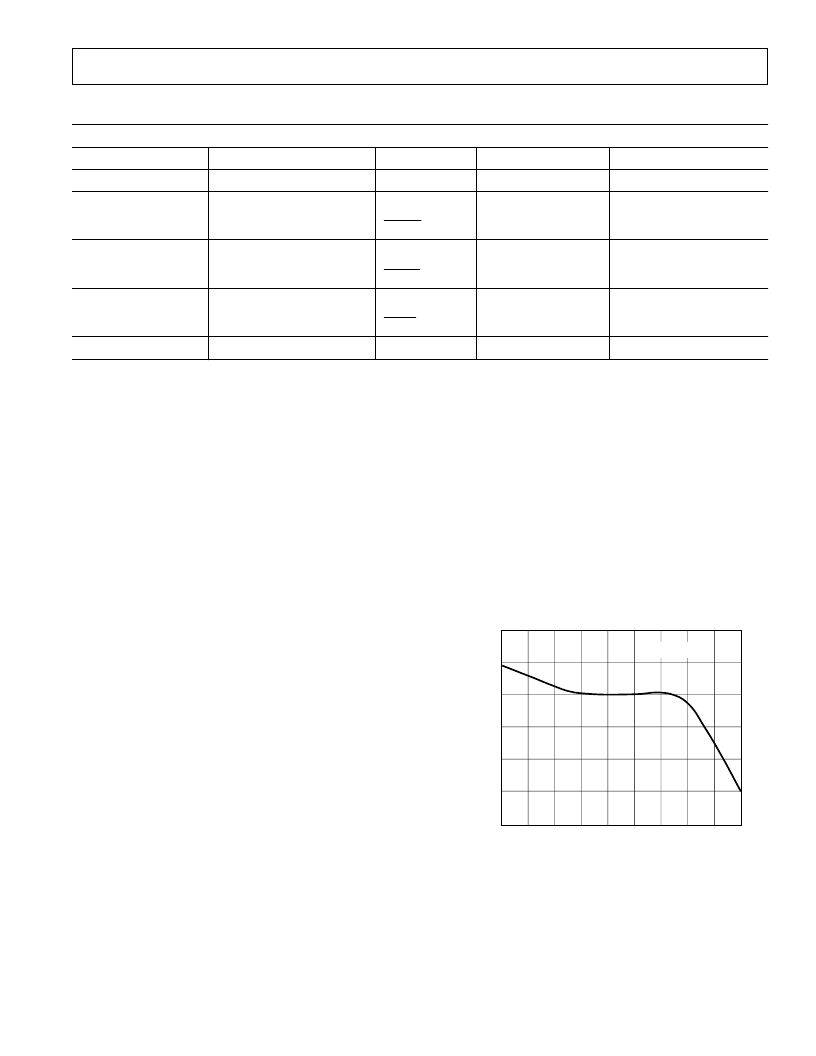

updated at a rate determined by the master clock, therefore the

amount of offset drift which occurs will be proportional to the

elapsed time between samples. T hus, to minimize offset drift at

higher temperatures, higher CLK IN rates are recommended.

Gain drift within the converter depends mainly upon the tem-

perature tracking of the internal capacitors. It is not affected by

leakage currents so that it is significantly less than offset drift.

T he typical gain drift of the AD7703 is less than 40 LSBs over

the specified temperature range.

Measurement errors due to offset drift or gain drift can be elimi-

nated at any time by recalibrating the converter. Using the sys-

tem calibration mode can also minimize offset and gain errors in

the signal conditioning circuitry. Integral and differential linear-

ity are not significantly affected by temperature changes.

B

160

0

–80

–160

–240

–320

–55

5

25

105

125

TEMPERATURE –

°

C

80

–35

–15

45

65

85

CLKIN = 4.096MHz

Figure 13. Typical Bipolar Offset vs. Temperature after

Calibration at +25

°

C

In the bipolar mode the system offset calibration range is

restricted to

±

0.4 V

REF

. It should be noted that the span

restrictions limit the amount of offset which can be calibrated.

T he span range of the converter in bipolar mode is equidistant

around the voltage used for the zero scale point. When the zero-

scale point is calibrated it must not cause either of the two

endpoints of the bipolar transfer function to exceed the positive

or the negative input overrange points (+V

REF

+ 0.1) V or

–V

REF

+ 0.1) V. If the span range is set to a minimum (0.8 V

REF

)

the offset voltage can move +0.4 V

REF

without causing the end

points of the transfer function to exceed the overrange points.

Alternatively, if the span range is set to 2 V

REF

, the input offset

cannot move more than +0.1 V or –0.1 V before an endpoint of

the transfer function exceeds the input overrange limit.

POWE R-UP AND CALIBRAT ION

A calibration cycle must be carried out after power-up to

initialize the device to a consistent starting condition and correct

calibration. T he CAL pin must be held high for at least four

clock cycles, after which calibration is initiated on the falling

edge of CAL and takes a maximum of 3,145,655 clock cycles

(approximately 768 ms with a 4.096 MHz clock). See T able III.

T he type of calibration cycle initiated by CAL is determined by

the SC1 and SC2 inputs, in accordance with T able III.

Drift Considerations

T he AD7703 uses chopper stabilization techniques to minimize

input offset drift. Charge injection in the analog switches and

leakage currents at the sampling node are the primary sources of

offset voltage drift in the converter. Figure 13 indicates the typi-

cal offset due to temperature changes after calibration at 25

°

C.

Drift is relatively flat up to 75

°

C. Above this temperature, leak-

age current becomes the main source of offset drift. Since leak-

age current doubles approximately every 10

°

C, the offset drifts

accordingly. T he value of the voltage on the sample capacitor is

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7703SQ | LC2MOS 20-Bit A/D Converter |

| AD7705 | 3 V/5 V, 1 mW 2-/3-Channel 16-Bit, Sigma-Delta ADCs |

| AD7705BN | ECONOLINE: REC2.2-S_DR/H1 - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- UL94V-0 Package Material- Continuous Short Circiut Protection- Internal SMD design- 100% Burned In- Efficiency to 75% |

| AD7705BR | ECONOLINE: REC2.2-S_DRW(Z)/H* - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- 4.5-9V, 9-18V, 18-36V, 36-72V Wide Input Range 2 : 1- UL94V-0 Package Material- Continuous Short Circiut Protection- Cost Effective- 100% Burned In- Efficiency to 84% |

| AD7705BRU | 3 V/5 V, 1 mW 2-/3-Channel 16-Bit, Sigma-Delta ADCs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7703CR-REEL | 功能描述:IC ADC 20BIT LC2MOS MONO 20-SOIC RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 位數(shù):14 采樣率(每秒):83k 數(shù)據(jù)接口:串行,并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應(yīng)商設(shè)備封裝:28-PDIP 包裝:管件 輸入數(shù)目和類型:1 個(gè)單端,雙極 |

| AD7703CRZ | 功能描述:IC ADC 20BIT LC2MOS MONO 20SOIC RoHS:是 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 位數(shù):14 采樣率(每秒):83k 數(shù)據(jù)接口:串行,并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應(yīng)商設(shè)備封裝:28-PDIP 包裝:管件 輸入數(shù)目和類型:1 個(gè)單端,雙極 |

| AD7703SQ | 制造商:AD 制造商全稱:Analog Devices 功能描述:LC2MOS 20-Bit A/D Converter |

| AD7705 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 1 mW 2-/3-Channel 16-Bit, Sigma-Delta ADCs |

| AD7705_06 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 1 mW, 2-/3-Channel, 16-Bit, Sigma-Delta ADCs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。