- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373914 > AD7706EB (Analog Devices, Inc.) High Performance Switched Capacitor Universal Filter; Package: PDIP; No of Pins: 14; Temperature Range: 0°C to +70°C PDF資料下載

參數(shù)資料

| 型號(hào): | AD7706EB |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | High Performance Switched Capacitor Universal Filter; Package: PDIP; No of Pins: 14; Temperature Range: 0°C to +70°C |

| 中文描述: | 3伏/ 5伏1毫瓦2-/3-Channel 16位Σ-Δ模數(shù)轉(zhuǎn)換器(264.12十一) |

| 文件頁(yè)數(shù): | 14/32頁(yè) |

| 文件大小: | 264K |

| 代理商: | AD7706EB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

AD7705/AD7706

–14–

REV. A

Data Register (RS2, RS1, RS0 = 0, 1, 1)

The Data Register on the part is a 16-bit read-only register that contains the most up-to-date conversion result from the AD7705/

AD7706. If the Communications Register sets up the part for a write operation to this register, a write operation must actually take

place to return the part to where it is expecting a write operation to the Communications Register. However, the 16 bits of data

written to the part will be ignored by the AD7705/AD7706.

Test Register (RS2, RS1, RS0 = 1, 0, 0); Power-On/Reset Status: 00Hex

The part contains a Test Register that is used when testing the device. The user is advised not to change the status of any of the bits

in this register from the default (Power-on or RESET) status of all 0s as the part will be placed in one of its test modes and will not

operate correctly.

Zero-Scale Calibration Register (RS2, RS1, RS0 = 1, 1, 0); Power-On/Reset Status: 1F4000Hex

The AD7705/AD7706 contains independent sets of zero-scale registers, one for each of the input channels. Each of these registers is

a 24-bit read/write register; 24 bits of data must be written otherwise no data will be transferred to the register. This register is used

in conjunction with its associated full-scale register to form a register pair. These register pairs are associated with input channel

pairs as outlined in Table VII. While the part is set up to allow access to these registers over the digital interface, the part itself no

longer has access to the register coefficients to correctly scale the output data. As a result, there is a possibility that after accessing the

calibration registers (either read or write operation) the first output data read from the part may contain incorrect data. In addition, a

write to the calibration register should not be attempted while a calibration is in progress. These eventualities can be avoided by

taking the FSYNC bit in the mode register high before the calibration register operation and taking it low after the operation is

complete.

Full-Scale Calibration Register (RS2, RS1, RS0 = 1, 1, 1); Power-On/Reset Status: 5761ABHex

The AD7705/AD7706 contains independent sets of full-scale registers, one for each of the input channels. Each of these registers is a

24-bit read/write register; 24 bits of data must be written otherwise no data will be transferred to the register. This register is used in

conjunction with its associated zero-scale register to form a register pair. These register pairs are associated with input channel pairs

as outlined in Table VII. While the part is set up to allow access to these registers over the digital interface, the part itself no longer

has access to the register coefficients to correctly scale the output data. As a result, there is a possibility that after accessing the cali-

bration registers (either read or write operation) the first output data read from the part may contain incorrect data. In addition, a

write to the calibration register should not be attempted while a calibration is in progress. These eventualities can be avoided by

taking FSYNC bit in the mode register high before the calibration register operation and taking it low after the operation is complete.

CALIBRATION SEQUENCES

The AD7705/AD7706 contains a number of calibration options as previously outlined. Table XIII summarizes the calibration types,

the operations involved and the duration of the operations. There are two methods of determining the end of calibration. The first is

to monitor when

DRDY

returns low at the end of the sequence.

DRDY

not only indicates when the sequence is complete, but also

that the part has a valid new sample in its data register. This valid new sample is the result of a normal conversion which follows the

calibration sequence. The second method of determining when calibration is complete is to monitor the MD1 and MD0 bits of the

Setup Register. When these bits return to 0 (0 following a calibration command), it indicates that the calibration sequence is com-

plete. This method does not give any indication of there being a valid new result in the data register. However, it gives an earlier

indication than

DRDY

that calibration is complete. The duration to when the Mode Bits (MD1 and MD0) return to 0 (0 represents

the duration of the calibration carried out). The sequence to when

DRDY

goes low also includes a normal conversion and a pipeline

delay, t

P

, to correctly scale the results of this first conversion. t

P

will never exceed 2000

×

t

CLKIN

. The time for both methods is given

in the table.

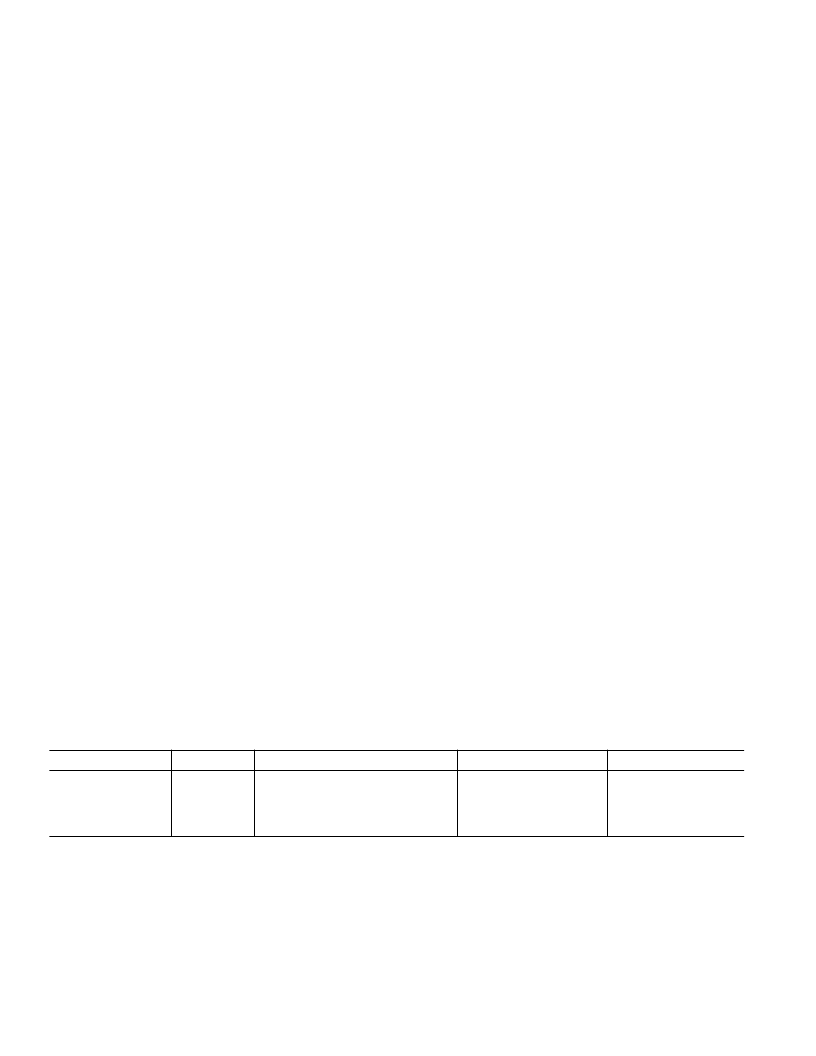

Table XIII. Calibration Sequences

C

alibration Type

MD1, MD0

Calibration Sequence

Duration to Mode Bits

Duration to

DRDY

Self-Calibration

0, 1

Internal ZS Cal @ Selected Gain +

Internal FS Cal @ Selected Gain

ZS Cal on AIN @ Selected Gain

FS Cal on AIN @ Selected Gain

6

×

1/Output Rate

9

×

1/Output Rate + t

P

ZS System Calibration

FS System Calibration

1, 0

1, 1

3

×

1/Output Rate

3

×

1/Output Rate

4

×

1/Output Rate + t

P

4

×

1/Output Rate + t

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7706(中文) | 3 V/5 V, 1 Mw 2-/3-Channel 16-Bit, Sigma-Delta ADCs(三輸入通道16位A/D轉(zhuǎn)換器) |

| AD7705(中文) | 3 V/5 V, 1 Mw 2-/3-Channel 16-Bit, Sigma-Delta ADCs(完全差分輸入通道16位A/D轉(zhuǎn)換器) |

| AD7707BR | 3 V/5 V, +-10 V Input Range, 1 mW 3-Channel 16-Bit, Sigma-Delta ADC |

| AD7707BRU | 3 V/5 V, +-10 V Input Range, 1 mW 3-Channel 16-Bit, Sigma-Delta ADC |

| AD7707 | ECONOLINE: REC2.2-S_DR/H1 - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- UL94V-0 Package Material- Continuous Short Circiut Protection- Internal SMD design- 100% Burned In- Efficiency to 75% |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7707 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, +-10 V Input Range, 1 mW 3-Channel 16-Bit, Sigma-Delta ADC |

| AD7707BR | 功能描述:IC ADC 16BIT 3CH 20-SOIC RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:- 位數(shù):12 采樣率(每秒):300k 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應(yīng)商設(shè)備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數(shù)目和類型:1 個(gè)單端,單極;1 個(gè)單端,雙極 |

| AD7707BR-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 500sps 16-bit Serial 20-Pin SOIC W T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.5KSPS 16BIT SERL 20SOIC W - Tape and Reel |

| AD7707BR-REEL7 | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 500sps 16-bit Serial 20-Pin SOIC W T/R 制造商:Analog Devices 功能描述:ADC SGL DELTA-SIGMA 0.5KSPS 16BIT SERL 20SOIC W - Tape and Reel |

| AD7707BRU | 功能描述:IC ADC 16BIT 3CH 20-TSSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:- 位數(shù):12 采樣率(每秒):300k 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應(yīng)商設(shè)備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數(shù)目和類型:1 個(gè)單端,單極;1 個(gè)單端,雙極 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。