- 您現在的位置:買賣IC網 > PDF目錄373914 > AD7707EB (Analog Devices, Inc.) 3 V/5 V 610 V Input Range 1 mW 3-Channel 16-Bit Sigma-Delta ADC(316.51 k) PDF資料下載

參數資料

| 型號: | AD7707EB |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 3 V/5 V 610 V Input Range 1 mW 3-Channel 16-Bit Sigma-Delta ADC(316.51 k) |

| 中文描述: | 3伏/ 5伏610 V輸入范圍1毫瓦3通道16位Σ-Δ模數轉換器(316.51十一) |

| 文件頁數: | 26/40頁 |

| 文件大小: | 316K |

| 代理商: | AD7707EB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

REV. A

AD7707

–26–

Reset Input

The

RESET

input on the AD7707 resets all the logic, the digital

filter and the analog modulator, while all on-chip registers are

reset to their default state.

DRDY

is driven high and the AD7707

ignores all communications to any of its registers while the

RESET

input is low. When the

RESET

input returns high, the

AD7707 starts to process data and

DRDY

will return low in 3

×

1/Output Rate indicating a valid new word in the data register.

However, the AD7707 operates with its default setup conditions

after a

RESET

and it is generally necessary to set up all registers

and carry out a calibration after a

RESET

command.

The AD7707’s on-chip oscillator circuit continues to function

even when the

RESET

input is low. The master clock signal

continues to be available on the MCLK OUT pin. Therefore, in

applications where the system clock is provided by the AD7707’s

clock, the AD7707 produces an uninterrupted master clock

during

RESET

commands.

Standby Mode

The STBY bit in the Communications Register of the AD7707

allows the user to place the part in a power-down mode when it

is not required to provide conversion results. The AD7707

retains the contents of all its on-chip registers (including the

data register) while in standby mode. When released from

standby mode, the part starts to process data and a new word is

available in the data register in 3

×

1/Output rate from when a 0

is written to the STBY bit.

The STBY bit does not affect the digital interface, nor does it

affect the status of the

DRDY

line. If

DRDY

is high when the

STBY bit is brought low, it will remain high until there is a valid

new word in the data register. If

DRDY

is low when the STBY

bit is brought low, it will remain low until the data register is

updated, at which time the

DRDY

line will return high for

500

×

t

CLKIN

before returning low again. If

DRDY

is low when

the part enters its standby mode (indicating a valid unread word

in the data register), the data register can be read while the part

is in standby. At the end of this read operation, the

DRDY

will

be reset high as normal.

Placing the part in standby mode reduces the total current to

9

μ

A typical with 5 V supplies and 4

μ

A with 3 V supplies when

the part is operated from an external master clock provided this

master clock is stopped. If the external clock continues to drive

the MCLK IN pin in standby mode, the standby current in-

creases to 150

μ

A typical with 5 V supplies and 75

μ

A typical

with 3 V supplies. If a crystal or ceramic resonator is used as the

clock source, the total current in standby mode is 400

μ

A typical

with 5 V supplies and 90

μ

A with 3 V supplies. This is because

the on-chip oscillator circuit continues to run when the part is in

its standby mode. This is important in applications where the

system clock is provided by the AD7707’s clock, so that the

AD7707 produces an uninterrupted master clock even when it is

in its standby mode. The serial interface remains operational

when in standby mode so that data can be read from the output

register in standby, regardless of whether or not the master clock

is stopped.

Accuracy

Sigma-Delta ADCs, like VFCs and other integrating ADCs, do

not contain any source of nonmonotonicity and inherently offer

no missing codes performance. The AD7707 achieves excellent

linearity by the use of high quality, on-chip capacitors, which

have a very low capacitance/voltage coefficient. The device also

achieves low input drift through the use of chopper-stabilized

techniques in its input stage. To ensure excellent performance

over time and temperature, the AD7707 uses digital calibration

techniques that minimize offset and gain error.

Drift Considerations

Charge injection in the analog switches and dc leakage currents

at the sampling modes are the primary sources of offset voltage

drift in the converter. The dc input leakage current is essentially

independent of the selected gain. Gain drift within the converter

depends primarily upon the temperature tracking of the internal

capacitors. It is not affected by leakage currents.

Measurement errors due to offset drift or gain drift can be elimi-

nated at any time by recalibrating the converter. Using the sys-

tem calibration mode can also minimize offset and gain errors in

the signal conditioning circuitry. Integral and differential linear-

ity errors are not significantly affected by temperature changes.

POWER SUPPLIES

The AD7707 operates with power supplies between 2.7 V and

5.25 V. There is no specific power supply sequence required for

the AD7707, either the AV

DD

or the DV

DD

supply can come up

first. In normal operation the DV

DD

must not exceed AV

DD

by

0.3 V. While the latch-up performance of the AD7707 is good,

it is important that power is applied to the AD7707 before sig-

nals at REFIN, AIN or the logic input pins in order to avoid

excessive currents. If this is not possible, the current that flows

in any of these pins should be limited to less than 100 mA. If

separate supplies are used for the AD7707 and the system digi-

tal circuitry, the AD7707 should be powered up first. If it is not

possible to guarantee this, current limiting resistors should be

placed in series with the logic inputs to again limit the current.

Latch-up current is greater than 100 mA.

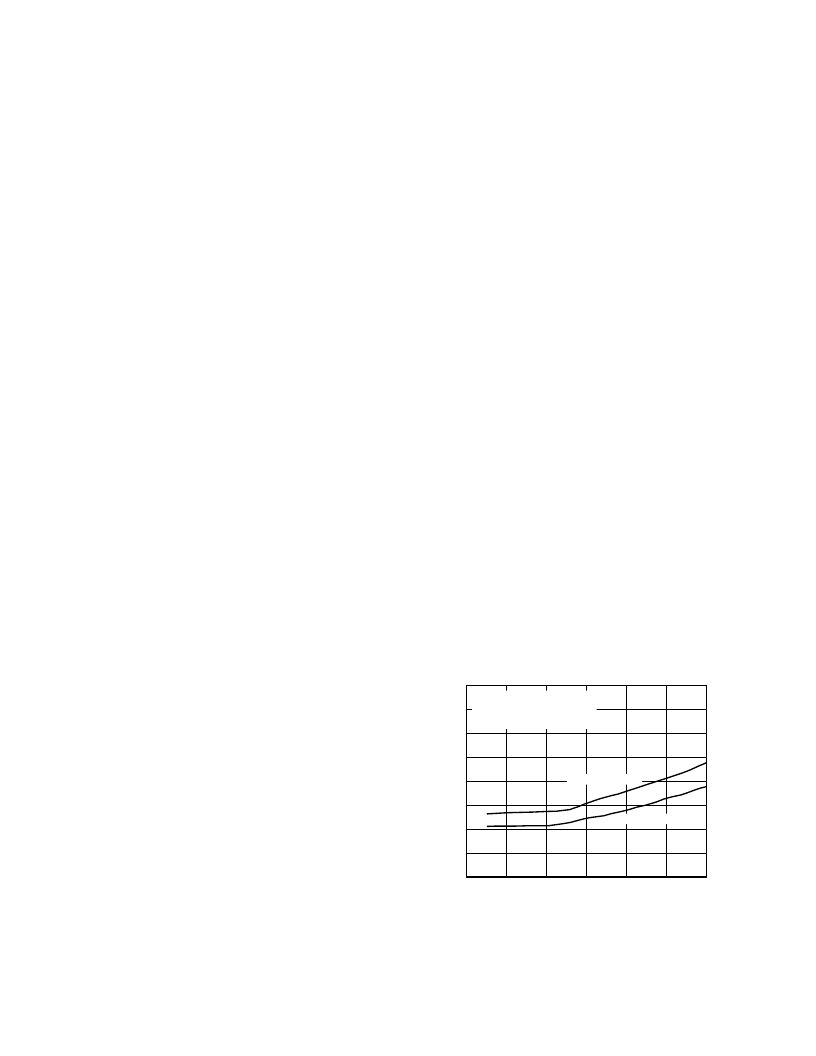

V

DD

1600

0

2.5

I

D

m

A

1400

800

600

400

200

1200

1000

5.5

3.0

3.5

4.0

4.5

5.0

USING CRYSTAL OSCILLATOR

T

= +25

8

C

UNBUFFERED MODE

GAIN = 128

f

CLK

= 2.4576MHz

f

CLK

= 1MHz

Figure 17. I

DD

vs. Supply Voltage

相關PDF資料 |

PDF描述 |

|---|---|

| AD7708BR | Shaft; Style: 2 - light; Applicable Model: LE-P / LEL-W |

| AD7708BRU | 8-/10-Channel, Low Voltage, Low Power, ADCs |

| AD7708 | 8-/10-Channel, Low Voltage, Low Power, ADCs |

| AD7718 | 8-/10-Channel, Low Voltage, Low Power, ADCs |

| AD7718BR | 8-/10-Channel, Low Voltage, Low Power, ADCs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7708 | 制造商:AD 制造商全稱:Analog Devices 功能描述:8-/10-Channel, Low Voltage, Low Power, ADCs |

| AD7708BR | 功能描述:IC ADC 16BIT R-R 8/10CH 28-SOIC RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:16 采樣率(每秒):45k 數據接口:串行 轉換器數目:2 功率耗散(最大):315mW 電壓電源:模擬和數字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數目和類型:2 個單端,單極 |

| AD7708BR-REEL | 功能描述:IC ADC 16BIT R-R 8/10CH 28-SOIC RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:16 采樣率(每秒):45k 數據接口:串行 轉換器數目:2 功率耗散(最大):315mW 電壓電源:模擬和數字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數目和類型:2 個單端,單極 |

| AD7708BR-REEL7 | 功能描述:IC ADC 16BIT R-R 8/10CH 28-SOIC RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:16 采樣率(每秒):45k 數據接口:串行 轉換器數目:2 功率耗散(最大):315mW 電壓電源:模擬和數字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數目和類型:2 個單端,單極 |

| AD7708BRU | 功能描述:IC ADC 16BIT R-R 8/10CH 28-TSSOP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:16 采樣率(每秒):45k 數據接口:串行 轉換器數目:2 功率耗散(最大):315mW 電壓電源:模擬和數字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數目和類型:2 個單端,單極 |

發布緊急采購,3分鐘左右您將得到回復。