- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373914 > AD7714* (Analog Devices, Inc.) 3 V/5 V. CMOS. 500 uA Signal Conditioning ADC PDF資料下載

參數(shù)資料

| 型號: | AD7714* |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 3 V/5 V. CMOS. 500 uA Signal Conditioning ADC |

| 中文描述: | 3 V / 5號五的CMOS。 500微安ADC的信號調(diào)理 |

| 文件頁數(shù): | 16/40頁 |

| 文件大?。?/td> | 306K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

AD7714

REV. C

–16–

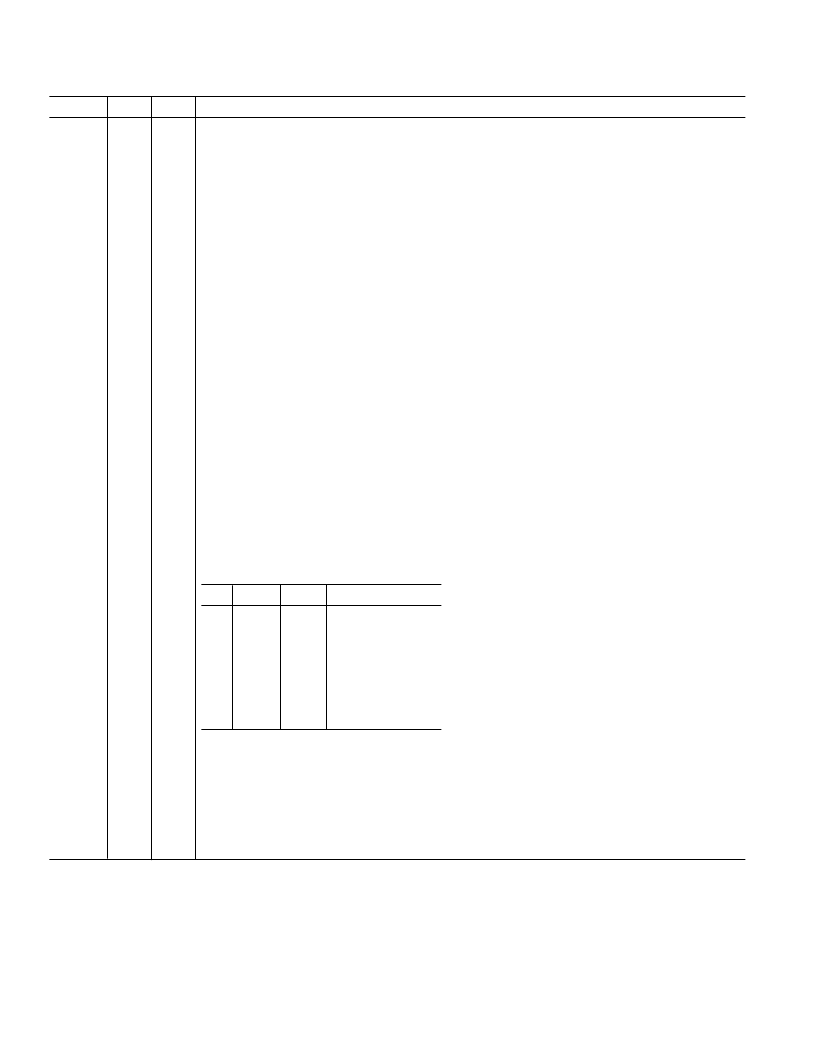

MD2

MD1

MD0

Operating Mode (continued)

1

0

0

System-Offset Calibration; this activates system-offset calibration on the channel selected by CH2, CH1

and CH0 of the Communications Register. This is a one step calibration sequence and when complete

the part returns to Normal Mode with MD2, MD1 and MD0 returning to 0, 0, 0. The

DRDY

output

or bit goes high when calibration is initiated and returns low when this system offset calibration is com-

plete and a new valid word is available in the data register. For this calibration type, the zero-scale cali-

bration is performed at the selected gain on the input voltage provided at the analog input during this

calibration sequence. This input voltage should remain stable for the duration of the calibration. The

full-scale calibration is performed at the selected gain on an internally generated V

REF

/Selected Gain.

Background Calibration; this activates background calibration on the channel selected by CH2, CH1

and CH0 of the Communications Register. If the background calibration mode is on, then the AD7714

provides continuous self-calibration of the shorted (zeroed) inputs. This calibration takes place as part

of the conversion sequence, extending the conversion time and reducing the word rate by a factor of six.

Its major advantage is that the user does not have to worry about recalibrating the offset of the device

when there is a change in the ambient temperature or supplies. In this mode, the zero-scale calibration

is performed at the selected gain on internally shorted (zeroed) inputs. The calibrations are interleaved

with normal conversions and the calibration registers of the device are automatically updated. Because

the background calibration does not perform full-scale calibrations, a self-calibration should be per-

formed before placing the part in the background calibration mode.

Zero-Scale Self-Calibration; this activates zero-scale self-calibration on the channel selected by CH2,

CH1 and CH0 of the Communications Register. This zero-scale self-calibration is performed at the

selected gain on internally shorted (zeroed) inputs. This is a one step calibration sequence and when

complete the part returns to Normal Mode with MD2, MD1 and MD0 returning to 0, 0, 0. The

DRDY

output or bit goes high when calibration is initiated and returns low when this zero-scale self-calibration

is complete and a new valid word is available in the data register.

Full-Scale Self-Calibration; this activates full-scale self-calibration on the channel selected by CH2,

CH1 and CH0 of the Communications Register. This full-scale self-calibration is performed at the

selected gain on an internally-generated V

REF

/Selected Gain. This is a one step calibration sequence and

when complete the part returns to Normal Mode with MD2, MD1 and MD0 returning to 0, 0, 0. The

DRDY

output or bit goes high when calibration is initiated and returns low when this full-scale self-

calibration is complete and a new valid word is available in the data register.

1

0

1

1

1

0

1

1

1

G2

G1

G0

Gain Setting

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1

2

4

8

16

32

64

128

BO

Burnout Current. A 0 in this bit turns off the on-chip burnout currents. This is the default (Power-On

or RESET) status of this bit. A 1 in this bit activates the burnout currents. When active, the burnout

currents connect to the selected analog input pair, one to the AIN(+) input and one to the AIN(–) input.

Filter Synchronization. When this bit is high, the nodes of the digital filter, the filter control logic and

the calibration control logic are held in a reset state and the analog modulator is also held in its reset

state. When this bit goes low, the modulator and filter start to process data and a valid word is available

in 3

×

1/(output update rate), i.e., the settling time of the filter. This FSYNC bit does not affect the

digital interface and does not reset the

DRDY

output if it is low.

FSYNC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7714ARS-3 | 3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714ARS-5 | 3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714ACHIPS-3 | 3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714ACHIPS-5 | 3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714YN | 3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7714ACHIPS-3 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714ACHIPS-5 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, CMOS, 500 uA Signal Conditioning ADC |

| AD7714AN-3 | 制造商:Rochester Electronics LLC 功能描述:24-BIT SIGMA DELTA A/D IC - Bulk 制造商:Analog Devices 功能描述: |

| AD7714AN5 | 制造商:ANA 功能描述:24 BIT, 1KSPS, DIP 24 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。