- 您現在的位置:買賣IC網 > PDF目錄373915 > AD7715* (Analog Devices, Inc.) 3 V/5 V. 450 uA 16-Bit. Sigma-Delta ADC PDF資料下載

參數資料

| 型號: | AD7715* |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 3 V/5 V. 450 uA 16-Bit. Sigma-Delta ADC |

| 中文描述: | 3 V / 5號五,450微安16位。 Σ-Δ模數轉換器 |

| 文件頁數: | 13/31頁 |

| 文件大小: | 474K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

AD7715

–13–

REV. C

AD7715-3

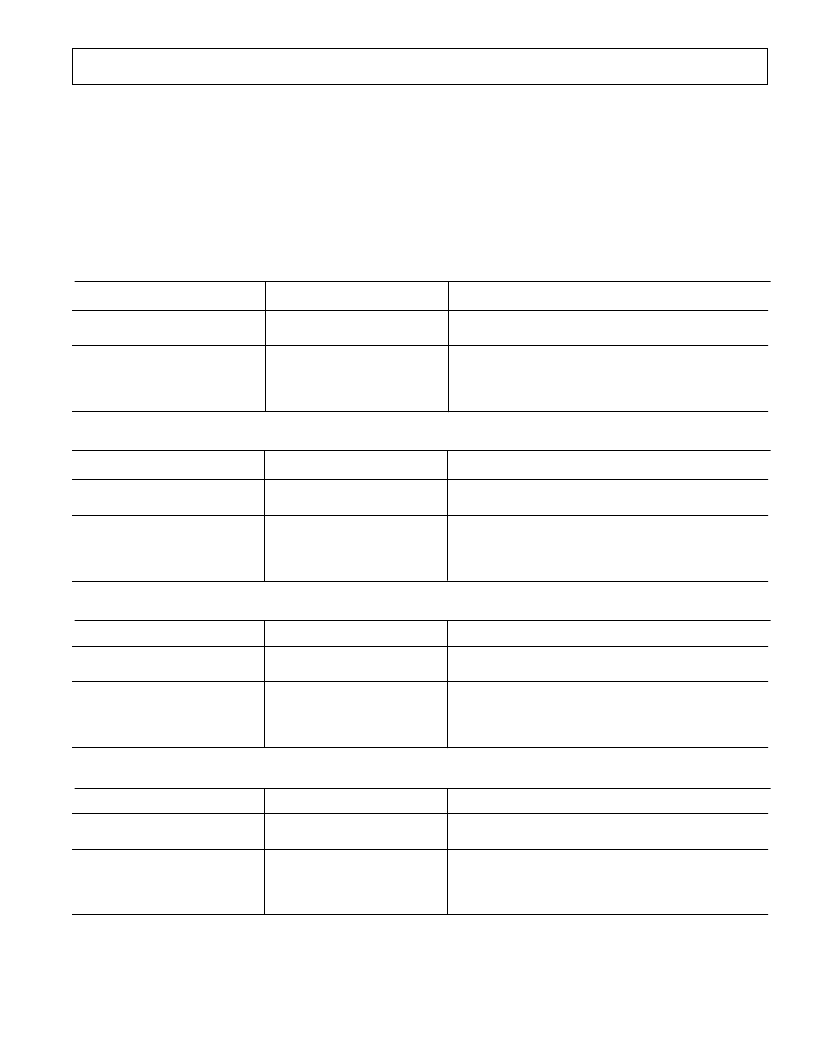

Table IX shows the AD7715-3 output rms noise for the selectable notch and –3dB frequencies for the part, as selected by FS1 and

FS0 of the Setup Register. The numbers given are for the bipolar input ranges with a V

REF

of +1.25V. These numbers are typical

and are generated at an analog input voltage of 0V with the part used in unbuffered mode (BUF bit of the Setup Register = 0).

Table X meanwhile shows the output

peak-to-peak

noise for the selectable notch and –3dB frequencies for the part.

It is important to

note that these numbers represent the resolution for which there will be no code flicker. They are not calculated based on rms noise but on peak-

to-peak noise

. The numbers given are for the bipolar input ranges with a V

REF

of +1.25V and for the BUF bit of the Setup Register =

0. These numbers are typical, are generated at an analog input voltage of 0V and are rounded to the nearest LSB.

Meanwhile, Table XI and Table XII show rms noise and peak-to-peak resolution respectively with the AD7715-3 operating under

the same conditions as above except that now the part is operating in buffered mode (BUF Bit of the Setup Register = 1).

Table IX. Output RMS Noise vs. Gain and Output Update Rate for AD7715-3 (Unbuffered Mode)

Filter First Notch & O/P Data Rate

–3dB Frequency

Typical Output RMS Noise in

m

V

MCLK IN =

2.4576 MHz

MCLK IN =

1 MHz

MCLK IN =

2.4576 MHz

MCLK IN =

1 MHz

GAIN = 1

GAIN = 2

GAIN = 32

GAIN = 128

50Hz

60Hz

250Hz

500Hz

20Hz

25Hz

100Hz

200Hz

13.1Hz

15.72Hz

65.5Hz

131Hz

5.24Hz

6.55Hz

26.2Hz

52.4Hz

3.0

3.4

45

270

1.7

2.1

20

135

0.7

0.7

2.2

9.7

0.65

0.7

1.6

3.3

Table X. Peak-to-Peak Resolution vs. Gain and Output Update Rate for AD7715-3 (Unbuffered Mode)

Filter First Notch & O/P Data Rate

–3dB Frequency

Typical Peak-to-Peak Resolution in Bits

MCLK IN =

2.4576 MHz

MCLK IN =

1 MHz

MCLK IN =

2.4576 MHz

MCLK IN =

1 MHz

GAIN = 1

GAIN = 2

GAIN = 32

GAIN = 128

50Hz

60Hz

250Hz

500Hz

20Hz

25Hz

100Hz

200Hz

13.1Hz

15.72Hz

65.5Hz

131Hz

5.24Hz

6.55Hz

26.2Hz

52.4Hz

16

16

13

11

16

16

13

11

14

14

13

10

12

12

11

10

Table XI. Output RMS Noise vs. Gain and Output Update Rate for AD7715-3 (Buffered Mode)

Filter First Notch & O/P Data Rate

–3dB Frequency

Typical Output RMS Noise in

m

V

MCLK IN =

2.4576 MHz

MCLK IN =

1 MHz

MCLK IN =

2.4576 MHz

MCLK IN =

1 MHz

GAIN = 1

GAIN = 2

GAIN = 32

GAIN = 128

50Hz

60Hz

250Hz

500Hz

20Hz

25Hz

100Hz

200Hz

13.1Hz

15.72Hz

65.5Hz

131Hz

5.24Hz

6.55Hz

26.2Hz

52.4Hz

4.5

5.1

50

270

2.4

2.9

25

135

0.9

0.9

2.6

9.7

0.9

1.0

2

3.3

Table XII. Peak-to-Peak Resolution vs. Gain and Output Update Rate for AD7715-3 (Buffered Mode)

Filter First Notch & O/P Data Rate

–3dB Frequency

Typical Peak-to-Peak Resolution in Bits

MCLK IN =

2.4576 MHz

MCLK IN =

1 MHz

MCLK IN =

2.4576 MHz

MCLK IN =

1 MHz

GAIN = 1

GAIN = 2

GAIN = 32

GAIN = 128

50Hz

60Hz

250Hz

500Hz

20Hz

25Hz

100Hz

200Hz

13.1Hz

15.72Hz

65.5Hz

131Hz

5.24Hz

6.55Hz

26.2Hz

52.4Hz

16

16

13

10

16

16

13

11

14

14

12

10

12

12

11

10

相關PDF資料 |

PDF描述 |

|---|---|

| AD7715ACHIPS-3 | 3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC |

| AD7715ACHIPS-5 | 3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC |

| AD7719BRU | Low Voltage, Low Power, Factory-Calibrated 16-/24-Bit Dual ADC |

| AD7719 | Low Voltage, Low Power, Factory-Calibrated 16-/24-Bit Dual ADC |

| AD7719BR | Low Voltage, Low Power, Factory-Calibrated 16-/24-Bit Dual ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7715_10 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 450 ??A 16-Bit, Sigma-Delta ADC |

| AD7715-5EB | 制造商:Analog Devices 功能描述: |

| AD7715ACHIPS-3 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC |

| AD7715ACHIPS-5 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC |

發布緊急采購,3分鐘左右您將得到回復。