- 您現在的位置:買賣IC網 > PDF目錄373915 > AD7721 (Analog Devices, Inc.) CMOS 16-Bit, 468.75 kHz, Sigma-Delta ADC PDF資料下載

參數資料

| 型號: | AD7721 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | CMOS 16-Bit, 468.75 kHz, Sigma-Delta ADC |

| 中文描述: | 的CMOS 16位,468.75千赫,Σ-Δ模數轉換器 |

| 文件頁數: | 13/16頁 |

| 文件大小: | 259K |

| 代理商: | AD7721 |

AD7721

REV. A

–13–

MICROCOMPUT E R/MICROPROCE SSOR INT E RFACING

T he AD7721 has a variety of interfacing options. It offers two

operating modes—serial and parallel.

Serial Interfacing

In serial mode, the AD7721 can be directly interfaced to several

DSPs. In all cases, the AD7721 operates as the master with the

DSP acting as the slave. T he AD7721 provides its own serial

clock to clock the digital word from the AD7721 to the DSP.

T he serial clock is a buffered version of the master clock CLK .

T he frame synchronization signal to the AD7721 and the DSP

is provided by the

DRDY

signal.

Because the serial clock from the AD7721 has the same frequency

as the master clock, DSPs that can accept high serial clock fre-

quencies are required. When the AD7721 is being operated

with a 15 MHz clock, Analog Devices’ ADSP-2106x SHARC

DSP is suitable as this DSP can accept very high serial clocks.

T he 40 MHz version of this DSP can accept a serial clock of

40 MHz maximum. T o interface the AD7721 to other DSPs,

the master clock frequency of the AD7721 can be reduced so

that it equals the maximum allowable frequency of the serial

clock for the DSP. T his will cause the sampling rate, the output

word rate and the bandwidth of the AD7721 to be reduced by a

proportional amount. T he ADSP-21xx family can operate with

a maximum serial clock of 13.824 MHz, the DSP56002 uses a

maximum serial clock of 13.3 MHz while the T MS320C5x-57

accepts a maximum serial clock of 10.989 MHz.

When the AD7721 is being operated with a low master clock

frequency (< 8 MHz), DSPs such as the T MS320C20/C25 and

DSP56000/1 can be used. Figures 13 to 15 show the interfaces

between the AD7721 and several DSPs. In all cases,

CS

,

RD

and

WR

are permanently hardwired to DGND.

AD7721 to ADSP-21xx Interface

Several of the ADSP-21xx family can interface directly to the

AD7721.

DRDY

is used as the frame sync signal for both the

ADSP-21xx and the AD7721.

DRDY

, which goes high for two

clock cycles when a conversion is complete, can also be used as

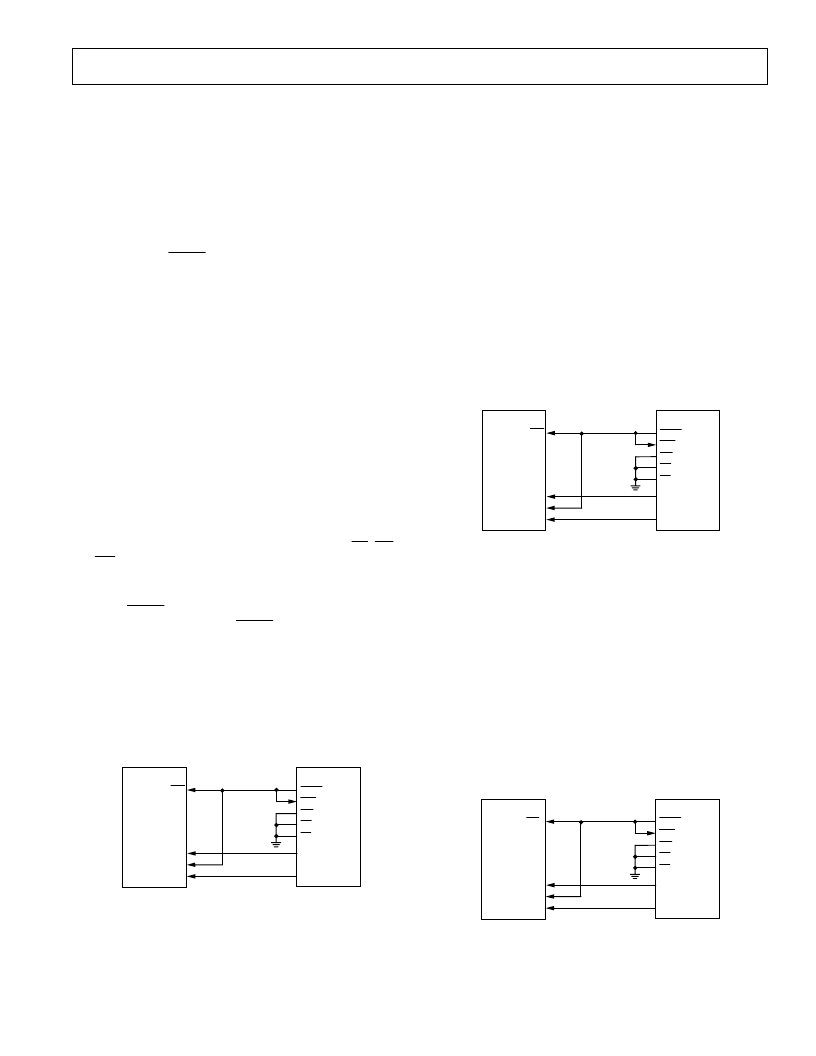

an interrupt signal if required. Figure 13 shows the AD7721

interface to the ADSP-21xx. For the ADSP-21xx, the bits in

the serial port control register should be set up as RFSR = 1

(a frame sync is needed for each transfer), SLEN = 15 (16 bit

word lengths), RFSW = 0 (normal framing mode for receive

operations), INVRFS = 0 (active high RFS), IRFS = 0 (external

RFS), and ISCLK = 0 (external serial clock).

AD7721

DRDY

RFS

ADSP-21xx

WR

RD

CS

DR

RFS

SCLK

SCLK

SDATA

IRQ

Figure 13. AD7721 to ADSP-21xx Interface

T he interface between the AD7721 and the ADSP-2106x

SHARC DSP is the same as shown in Figure 13, but the DSP is

configured as follows: SLEN = 15 (16-bit word transfers),

SENDN = 0 (the MSB of the 16-bit word will be received by

the DSP first), ICLK = 0 (an external serial clock will be used),

RFSR = 0 (a frame sync is required for every word transfer),

IRFS = 0 (the receive frame sync signal is external), CK RE = 0

(the receive data will be latched into the DSP on the falling

clock edge), LAFS = 0 (the DSP begins reading the 16 bit word

after the DSP has identified the frame sync signal rather than

the DSP reading the word at the same instant as the frame sync

signal has been identified), LRFS = 0 (RFS is active high).

AD7721 to DSP56002 Interface

Figure 14 shows the AD7721 to DSP56002 interface. If the

AD7721 is being used at a lower clock frequency (

≤

5.128 MHz),

the DSP56000 or DSP56001 can be used. T he interface will be

similar for all three DSPs. T o interface the DSP56002 to the

AD7721, the DSP56002 is configured as follows: SY N = 1

(synchronous mode), SCD1 = 0 (RFS will be an input),

GCK = 0 (a continuous clock will be used), SCK D = 0 (the

serial clock will be external), WL1 = 1, WL0 = 0 (transfers will

be 16 bits wide), FSL1 = 0, FSL0 = 1 (the frame sync will be

active at the beginning of each transfer).

AD7721

DRDY

RFS

DSP56002

WR

RD

CS

SRD

SC1

SCK

SCLK

SDATA

IRQ

Figure 14. AD7721 to DSP56002 Interface

Alternatively, the DSP56002 can be operated in asynchronous

mode (SYN = 0). In this mode, the serial clock for the Receive

section in inputted to the SC0 pin. T his is accomplished by

setting bit SCD0 to 0 (external Rx clock).

AD7721 to T MS320C20/C25/C5x Interface

Figure 15 shows the AD7721 to T MS320C20/C25/C5x inter-

face. For the T MS320C5x, FSR and CLK R are automatically

configured as inputs. T he serial port is configured as follows:

FO = 0 (16-bit word transfers), FSM = 1 (a frame sync occurs

for each transfer). Figure 15 shows the interface diagram when

the AD7721 is being interfaced to the T MS320C20 and the

T MS320C25 also but, these DSPs can be used only when the

AD7721 is being used at a lower frequency such as 5 MHz

(C25) or 2.56 MHz (C20).

AD7721

DRDY

RFS

WR

RD

CS

SCLK

SDATA

TMS320C

20/25/5x

DR

FSR

CLKR

INT0

Figure 15. AD7721 to TMS320C20/25/5x Interface

SHARC is a registered trademark of Analog Devices, Inc.

相關PDF資料 |

PDF描述 |

|---|---|

| AD7721AN | CMOS 16-Bit, 468.75 kHz, Sigma-Delta ADC |

| AD7721AR | CMOS 16-Bit, 468.75 kHz, Sigma-Delta ADC |

| AD7721SQ | CMOS 16-Bit, 468.75 kHz, Sigma-Delta ADC |

| AD7722 | 16-Bit, 195 kSPS CMOS, Sigma-Delta ADC |

| AD7722AS | 16-Bit, 195 kSPS CMOS, Sigma-Delta ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7721AN | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 468.75ksps 16-bit Parallel/Serial 28-Pin PDIP W |

| AD7721ANZ | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 468.75ksps 16-bit Parallel/Serial 28-Pin PDIP W |

| AD7721AR | 功能描述:IC ADC 16BIT SIGMA-DELTA 28-SOIC RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:12 采樣率(每秒):300k 數據接口:并聯 轉換器數目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數目和類型:1 個單端,單極;1 個單端,雙極 |

| AD7721AR-REEL | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 468.75ksps 16-bit Parallel/Serial 28-Pin SOIC W T/R |

| AD7721ARZ | 功能描述:IC ADC 16BIT SIGMA-DELTA 28SOIC RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 其它有關文件:TSA1204 View All Specifications 標準包裝:1 系列:- 位數:12 采樣率(每秒):20M 數據接口:并聯 轉換器數目:2 功率耗散(最大):155mW 電壓電源:模擬和數字 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-TQFP 供應商設備封裝:48-TQFP(7x7) 包裝:Digi-Reel® 輸入數目和類型:4 個單端,單極;2 個差分,單極 產品目錄頁面:1156 (CN2011-ZH PDF) 其它名稱:497-5435-6 |

發布緊急采購,3分鐘左右您將得到回復。