- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373916 > AD7742BR (ANALOG DEVICES INC) Single and Multichannel, Synchronous Voltage-to-Frequency Converters PDF資料下載

參數(shù)資料

| 型號: | AD7742BR |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 模擬專用變換器 |

| 英文描述: | Single and Multichannel, Synchronous Voltage-to-Frequency Converters |

| 中文描述: | VOLTAGE-FREQUENCY CONVERTER, 6.144 MHz, PDSO16 |

| 封裝: | SOIC-16 |

| 文件頁數(shù): | 3/12頁 |

| 文件大小: | 131K |

| 代理商: | AD7742BR |

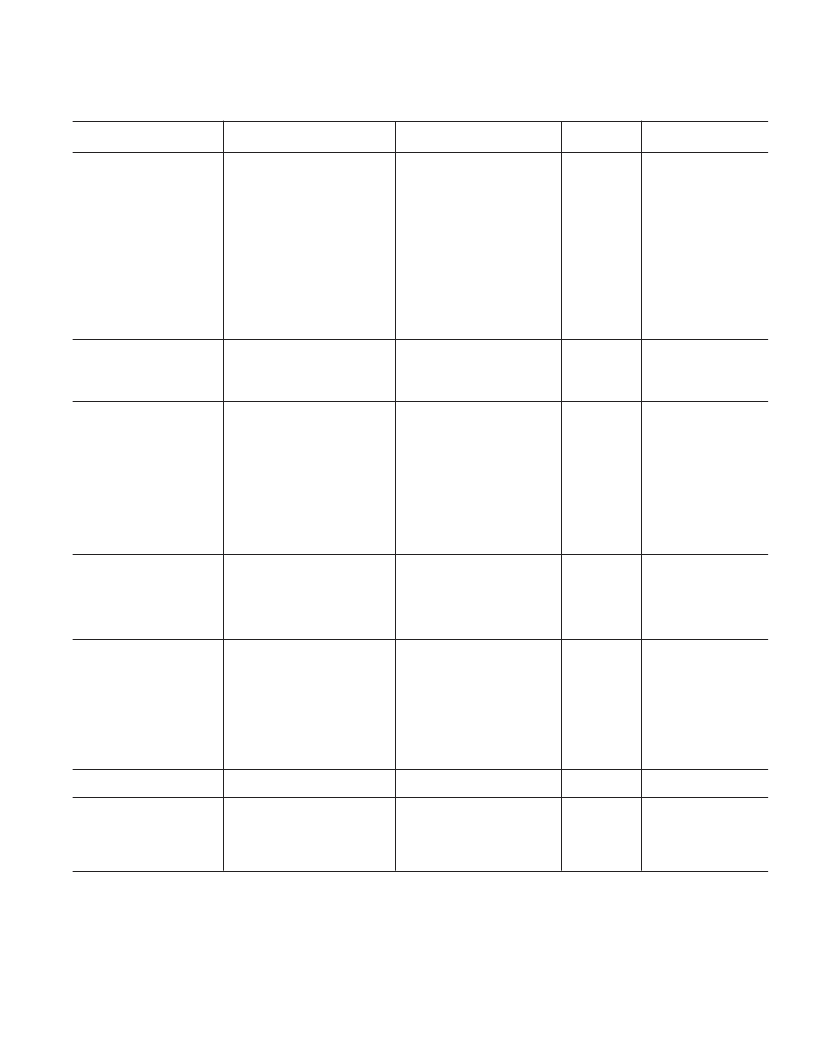

REV. 0

–3–

AD7741/AD7742

(V

DD

= +4.75 V to +5.25 V; V

REF

= +2.5 V; f

CLKIN

= 6.144 MHz; all specifications T

MIN

to

T

MAX

unless otherwise noted.)

B Version

1

Y Version

2

Min

Parameter

3

Min

Typ

Max

Typ

Max

Units

Conditions/Comments

DC PERFORMANCE

Integral Nonlinearity

f

CLKIN

= 200 kHz

4

f

CLKIN

= 3 MHz

4

f

= 6.144 MHz

Offset Error

±

0.0122

±

0.0122

±

0.0122

±

40

±

40

+2.2

+2.2

±

0.015

±

0.015

±

0.015

±

40

±

40

+2.2

+2.2

% of Span

5

% of Span

% of Span

mV

mV

% of Span

% of Span

μ

V/

°

C

μ

V/

°

C

ppm of Span/

°

C

ppm of Span/

°

C

dB

dB

dB

Unipolar Mode

Bipolar Mode

Unipolar Mode

Bipolar Mode

Unipolar Mode

Bipolar Mode

Unipolar Mode

Bipolar Mode

V

DD

=

±

5%

Gain Error

+0.2

+0.2

+1.2

+1.2

±

12

±

12

±

2

±

4

–70

–75

–78

+0.2

+0.2

+1.2

+1.2

±

12

±

12

±

2

±

4

–70

–75

–78

Offset Error Drift

4

Gain Error Drift

4

Power Supply Rejection Ratio

4

Channel-to-Channel Isolation

4

Common-Mode Rejection

ANALOG INPUTS (V

IN

1–V

IN

4)

6

Input Current

Common-Mode Input Range

Differential Input Range

–60

–58

±

50

±

100

V

DD

– 1.75

+V

REF

/Gain –V

REF

/Gain

+V

REF

/Gain 0

±

50

±

100

V

DD

– 1.75

+V

REF

/Gain

+V

REF

/Gain

nA

V

V

V

+0.5

–V

REF

/Gain

0

+0.5

Bipolar Mode

Unipolar Mode

VOLTAGE REFERENCE

REFIN

Nominal Input Voltage

Input Impedance

f

CLKIN

= 3 MHz

f

= 6.144 MHz

REFOUT

Output Voltage

Output Impedance

4

Reference Drift

Line Rejection

Reference Noise

(0.1 Hz to 10 Hz)

4

2.5

2.5

V

70

35

70

35

k

k

2.38

2.50

1

±

50

–70

2.60

2.38

2.50

1

±

50

–70

2.60

V

k

ppm/

°

C

dB

100

100

μ

V p-p

LOGIC OUTPUT

Output High Voltage, V

OH

Output Low Voltage, V

Minimum Output Frequency

4.0

4.0

V

V

Hz

Output Sourcing 800

μ

A

7

Output Sinking 1.6 mA

7

V

IN

= 0 V (Unipolar), V

IN

=

–V

REF

/Gain (Bipolar)

V

/Gain (Unipolar

and Bipolar)

0.4

0.4

0.05 f

CLKIN

0.05 f

CLKIN

Maximum Output Frequency

0.45 f

CLKIN

0.45 f

CLKIN

Hz

LOGIC INPUT

ALL EXCEPT CLKIN

Input High Voltage, V

IH

Input Low Voltage, V

IL

Input Current

Pin Capacitance

CLKIN ONLY

Input High Voltage, V

IH

Input Low Voltage, V

IL

Input Current

Pin Capacitance

2.4

2.4

V

V

nA

pF

0.8

±

100

10

0.8

±

100

10

6

6

3.5

3.5

V

V

μ

A

pF

0.8

±

2

10

0.8

±

2

10

6

6

CLOCK FREQUENCY

Input Frequency

6.144

6.144

MHz

For Specified Performance

POWER REQUIREMENTS

V

DD

I

DD

(Normal Mode)

I

(Power-Down)

Power-Up Time

4.75

5.25

8

35

4.75

5.25

8

35

V

mA

μ

A

μ

s

6

25

30

6

25

30

Output Unloaded

Coming Out of Power-

Down Mode

N

OTES

1

Temperature range: B Version: –40

°

C to +85

°

C.

2

Temperature range: Y Version: –40

°

C to +105

°

C.

3

See Terminology.

4

Guaranteed by design and characterization, not production tested.

5

Span = Maximum Output Frequency–Minimum Output Frequency.

6

The absolute voltage on the input pins must not go more positive than V

– 1.75 V or more negative than +0.5 V.

7

These logic levels apply to CLKOUT only when it is loaded with one CMOS load.

Specifications subject to change without notice

.

AD7742–SPECIFICATIONS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD774BJR | Complete 12-Bit A/D Converters |

| AD774BAR | Complete 12-Bit A/D Converters |

| AD774BBR | Complete 12-Bit A/D Converters |

| AD774BAD | Complete 12-Bit A/D Converters |

| AD774BBD | Complete 12-Bit A/D Converters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7742BR-REEL | 制造商:Analog Devices 功能描述: |

| AD7742YR | 制造商:AD 制造商全稱:Analog Devices 功能描述:Single and Multichannel, Synchronous Voltage-to-Frequency Converters |

| AD7742YR-REEL | 制造商:Analog Devices 功能描述: |

| AD7742YR-REEL7 | 制造商:Analog Devices 功能描述: |

| AD7742YRZ | 制造商:Analog Devices 功能描述:VFC Sync 2.75MHz 16-Pin SOIC N |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。