- 您現在的位置:買賣IC網 > PDF目錄373921 > AD7865AS-1 (ANALOG DEVICES INC) Four-Channel, Simultaneous Sampling, Fast, 14-Bit ADC PDF資料下載

參數資料

| 型號: | AD7865AS-1 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | Four-Channel, Simultaneous Sampling, Fast, 14-Bit ADC |

| 中文描述: | 4-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PQFP44 |

| 封裝: | PLASTIC, QFP-44 |

| 文件頁數: | 4/19頁 |

| 文件大小: | 195K |

| 代理商: | AD7865AS-1 |

AD7865

TIMING CHARACTERISTICS

1, 2

–4–

REV. A

Parameter

A, B, Y Versions

Units

μ

s max

μ

s max

μ

s max

Test Conditions/Comments

t

CONV

2.4

3.2

0.35

No. of Channels

×

(t

CONV

)

1

35

70

Conversion Time, Internal Clock

Conversion Time, External Clock (5 MHz)

Acquisition Time

Selected Number of Channels Multiplied by t

CONV

t

ACQ

t

BUSY

μ

s max

μ

s max

ns min

ns min

t

WAKE-UP

—External V

REF3

t

1

t

2

Read Operation

t

3

t

4

t

5

t

64

STBY

Rising Edge to

CONVST

Rising Edge

CONVST

Pulsewidth

CONVST

Rising Edge to BUSY Rising Edge

0

0

35

35

40

5

30

15

120

180

70

15

0

ns min

ns min

ns min

ns max

ns max

ns min

ns max

ns min

ns min

ns max

ns max

ns max

ns min

CS

to

RD

Setup Time

CS

to

RD

Hold Time

Read Pulsewidth

Data Access Time After Falling Edge of

RD

, V

DRIVE

= 5 V

Data Access Time After Falling Edge of

RD

, V

DRIVE

= 3 V

Bus Relinquish Time After Rising Edge of

RD

t

75

t

8

t

9

Time Between Consecutive Reads

EOC

Pulsewidth

t

10

t

11

t

12

RD

Rising Edge to FRSTDATA Edge (Rising or Falling)

EOC

Falling Edge to FRSTDATA Falling Delay

EOC

to

RD

Delay

Write Operation

t

13

t

14

t

15

t

16

t

17

External Clock

t

18

20

0

0

5

5

ns min

ns min

ns min

ns min

ns min

WR

Pulsewidth

CS

to

WR

Setup Time

WR

to

CS

Hold Time

Input Data Setup Time of Rising Edge of

WR

Input Data Hold Time

200

ns min

CONVST

Falling Edge to CLK Rising Edge

NOTES

1

Sample tested at +25

°

C to ensure compliance. All input signals are measured with tr = tf = 1 ns (10% to 90% of +5 V) and timed from a voltage level of +1.6V.

2

See Figures 6, 7 and 8.

3

Refer to the Standby Mode Operation section. The MAX specification of 1

μ

s is valid when using a 0.1

μ

F decoupling capacitor on the V

REF

pin.

4

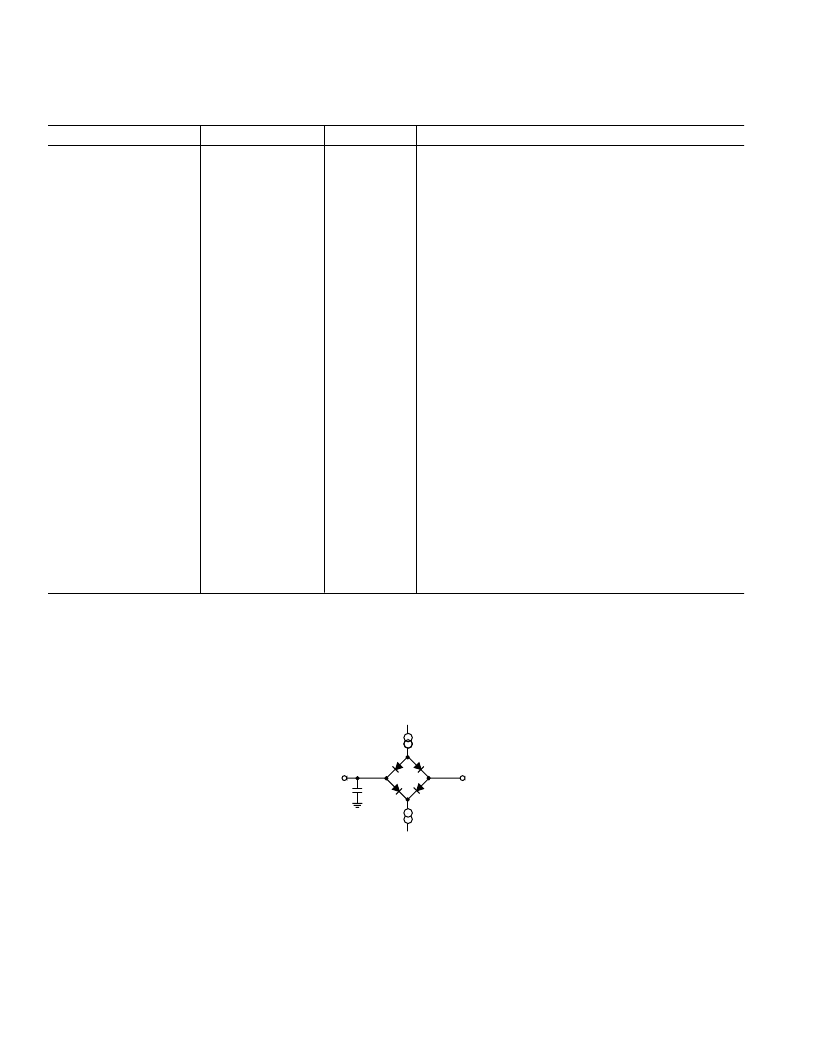

Measured with the load circuit of Figure 1 and defined as the time required for an output to cross 0.8V or 2.4 V.

5

These times are derived from the measured time taken by the data outputs to change 0.5V when loaded with the circuit of Figure 1. The measured number is then

extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus

relinquish times of the part and as such are independent of external bus loading capacitances.

Specifications subject to change without notice.

1.6mA

50pF

TO OUTPUT

PIN

+1.6V

400

m

A

Figure 1. Load Circuit for Access Time and Bus Relinquish Time

(V

DD

= +5 V

6

5%, AGND = DGND = 0 V, V

REF

= Internal, Clock = Internal; all specifications

T

MIN

to T

MAX

unless otherwise noted.)

相關PDF資料 |

PDF描述 |

|---|---|

| AD7865AS-2 | Four-Channel, Simultaneous Sampling, Fast, 14-Bit ADC |

| AD7865AS-3 | Four-Channel, Simultaneous Sampling, Fast, 14-Bit ADC |

| AD7865BS-1 | Four-Channel, Simultaneous Sampling, Fast, 14-Bit ADC |

| AD7865BS-2 | Four-Channel, Simultaneous Sampling, Fast, 14-Bit ADC |

| AD7865BS-3 | Four-Channel, Simultaneous Sampling, Fast, 14-Bit ADC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7865AS-1REEL | 制造商:Analog Devices 功能描述:ADC Single SAR 350ksps 14-bit Parallel 44-Pin MQFP T/R 制造商:Rochester Electronics LLC 功能描述:4 CH. SIMULTANEOUS BIPOLAR,14-B ADC I.C. - Tape and Reel |

| AD7865AS2 | 制造商:AD 功能描述:* |

| AD7865AS-2 | 制造商:Analog Devices 功能描述:ADC Single SAR 350ksps 14-bit Parallel 44-Pin MQFP 制造商:Analog Devices 功能描述:IC 14-BIT ADC |

| AD7865AS-2REEL | 制造商:Analog Devices 功能描述:ADC Single SAR 350ksps 14-bit Parallel 44-Pin MQFP T/R 制造商:Analog Devices 功能描述:ADC SGL SAR 350KSPS 14BIT PARALLEL 44MQFP - Tape and Reel |

| AD7865AS-3 | 制造商:Analog Devices 功能描述:ADC Single SAR 350ksps 14-bit Parallel 44-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:4 CH. SIMULTANEOUS BIPOLAR,14-B ADC I.C. - Bulk 制造商:Analog Devices 功能描述:IC 14-BIT ADC |

發布緊急采購,3分鐘左右您將得到回復。