- 您現在的位置:買賣IC網 > PDF目錄373926 > AD7921ARM (ANALOG DEVICES INC) 2-Channel, 2.35 V to 5.25 V 250 kSPS, 10-/12-Bit ADCs PDF資料下載

參數資料

| 型號: | AD7921ARM |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 2-Channel, 2.35 V to 5.25 V 250 kSPS, 10-/12-Bit ADCs |

| 中文描述: | 2-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| 封裝: | MO-187AA, MSOP-8 |

| 文件頁數: | 21/28頁 |

| 文件大小: | 312K |

| 代理商: | AD7921ARM |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

AD7911/AD7921

SERIAL INTERFACE

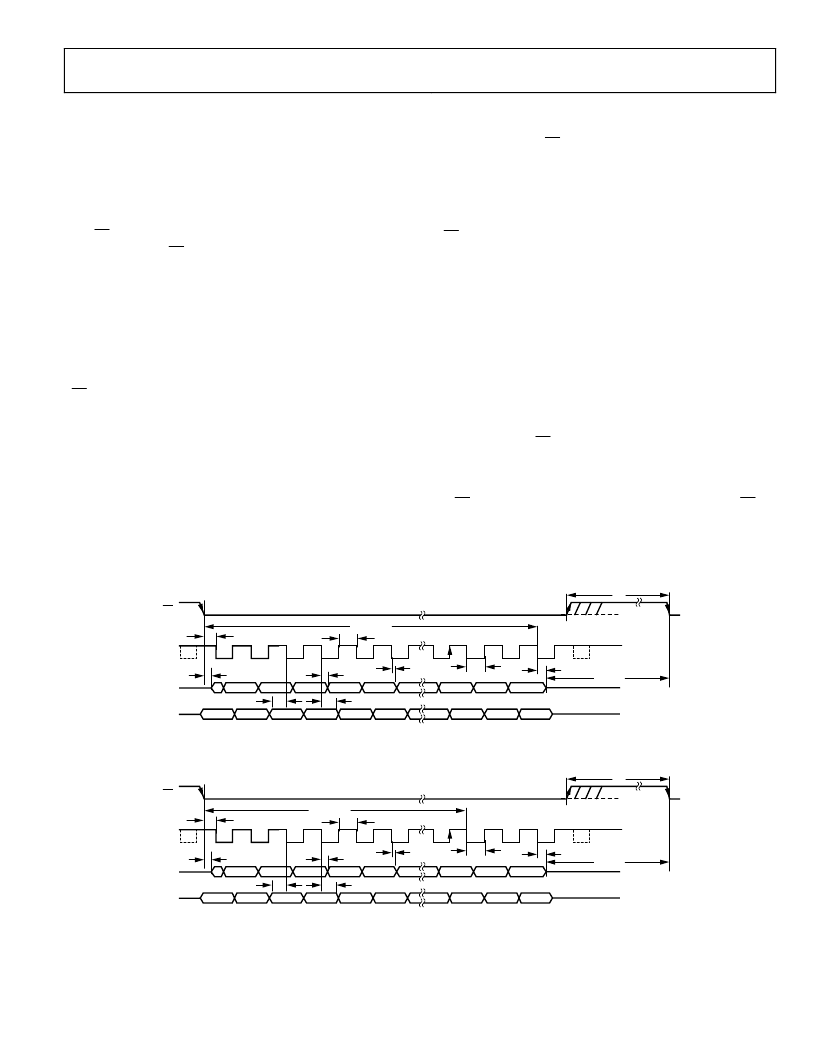

Figure 30 and Figure 31 show the detailed timing diagrams for

serial interfacing to the AD7921 and AD7911, respectively. The

serial clock provides the conversion clock and also controls the

transfer of information from the AD7911/AD7921 during

conversion.

Rev. 0 | Page 21 of 28

The CS signal initiates the data transfer and conversion process.

The falling edge of CS puts the track-and-hold into hold mode,

takes the bus out of three-state, the analog input is sampled at

this point, and the conversion is initiated.

For the AD7921, the conversion requires 16 SCLK cycles to

complete. Once 13 SCLK falling edges have elapsed, the track-

and-hold goes back into track on the next SCLK rising edge, as

shown in Figure 30 at Point B. On the 16th SCLK falling edge,

the DOUT line goes back into three-state. If the rising edge of

CS occurs before 16 SCLKs have elapsed, then the conversion is

terminated and the DOUT line goes back into three-state.

Otherwise, DOUT returns to three-state on the 16th SCLK

falling edge, as shown in Figure 30. Sixteen serial clock cycles

are required to perform the conversion process and to access

data from the AD7921.

For the AD7911, the conversion requires 14 SCLK cycles to

complete. Once 13 SCLK falling edges have elapsed, the track-

and-hold goes back into track on the next SCLK rising edge, as

shown in Figure 31 at Point B.

If the rising edge of CS occurs before 14 SCLKs have elapsed,

then the conversion is terminated and the DOUT line goes back

into three-state. If 16 SCLKs are considered in the cycle, DOUT

returns to three-state on the 16th SCLK falling edge, as shown

in Figure 31.

CS going low clocks out the first leading zero to be read in by

the microcontroller or DSP. The remaining data is then clocked

out by subsequent SCLK falling edges beginning with the

second leading zero. Therefore, the first falling clock edge on

the serial clock has the first leading zero provided and also

clocks out the second leading zero. The final bit in the data

transfer is valid on the 16th falling edge, having been clocked

out on the previous (15th) falling edge.

In applications with a slower SCLK, it is possible to read in data

on each SCLK rising edge. In that case, the first falling edge of

SCLK clocks out the second leading zero and it can be read in

the first rising edge. However, the first leading zero that is

clocked out when CS goes low is missed, unless it is not read in

the first falling edge. The 15th falling edge of SCLK clocks out

the last bit and it can be read in the 15th rising SCLK edge.

If CS goes low just after the SCLK falling edge has elapsed, CS

clocks out the first leading zero as before and it can be read in

the SCLK rising edge. The next SCLK falling edge clocks out

the second leading zero and it can be read in the following

rising edge.

0

ZERO

X

1

2

3

4

5

13

14

t

5

15

16

X

CHN

X

X

X

X

X

X

CHN

X

DB11

DB10

DB2

DB1

DB0

Z

t

2

t

6

t

4

t

8

t

9

t

3

t

7

t

10

t

1

t

QUIET

t

CONVERT

SCLK

CS

DOUT

THREE-STATE

THREE-STATE

DIN

B

Figure 30. AD7921 Serial Interface Timing Diagram

0

ZERO

X

1

2

3

4

5

13

14

t

5

15

16

X

CHN

X

X

X

X

X

X

CHN

X

DB9

DB8

DB0

TWO TRAILING ZEROS

ZERO

ZERO

Z

t

2

t

6

t

4

t

8

t

9

t

3

t

7

t

10

t

1

t

QUIET

t

CONVERT

SCLK

CS

DOUT

THREE-STATE

THREE-STATE

DIN

B

Figure 31. AD7911 Serial Interface Timing Diagram

相關PDF資料 |

PDF描述 |

|---|---|

| AD7921ARM-REEL | 2-Channel, 2.35 V to 5.25 V 250 kSPS, 10-/12-Bit ADCs |

| AD7921ARM-REEL7 | 2-Channel, 2.35 V to 5.25 V 250 kSPS, 10-/12-Bit ADCs |

| AD7921AUJ-R2 | 2-Channel, 2.35 V to 5.25 V 250 kSPS, 10-/12-Bit ADCs |

| AD7921AUJ-REEL7 | 2-Channel, 2.35 V to 5.25 V 250 kSPS, 10-/12-Bit ADCs |

| AD7911 | 2-Channel, 2.35 V to 5.25 V 250 kSPS, 10-/12-Bit ADCs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7921ARM-REEL | 制造商:Analog Devices 功能描述:ADC Single SAR 250ksps 12-bit Serial 8-Pin MSOP T/R 制造商:Analog Devices 功能描述:ADC SGL SAR 250KSPS 12-BIT SERL 8MSOP - Tape and Reel 制造商:Rochester Electronics LLC 功能描述:DUAL 12-BIT , 250KSPS ADC I.C. - Tape and Reel |

| AD7921ARM-REEL7 | 功能描述:IC ADC 12BIT DUAL LP 8-MSOP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:microPOWER™ 位數:8 采樣率(每秒):1M 數據接口:串行,SPI? 轉換器數目:1 功率耗散(最大):- 電壓電源:模擬和數字 工作溫度:-40°C ~ 125°C 安裝類型:表面貼裝 封裝/外殼:24-VFQFN 裸露焊盤 供應商設備封裝:24-VQFN 裸露焊盤(4x4) 包裝:Digi-Reel® 輸入數目和類型:8 個單端,單極 產品目錄頁面:892 (CN2011-ZH PDF) 其它名稱:296-25851-6 |

| AD7921ARMZ | 功能描述:IC ADC 12BIT DUAL LP 8-MSOP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:microPOWER™ 位數:8 采樣率(每秒):1M 數據接口:串行,SPI? 轉換器數目:1 功率耗散(最大):- 電壓電源:模擬和數字 工作溫度:-40°C ~ 125°C 安裝類型:表面貼裝 封裝/外殼:24-VFQFN 裸露焊盤 供應商設備封裝:24-VQFN 裸露焊盤(4x4) 包裝:Digi-Reel® 輸入數目和類型:8 個單端,單極 產品目錄頁面:892 (CN2011-ZH PDF) 其它名稱:296-25851-6 |

| AD7921ARMZ-REEL | 功能描述:IC ADC 12BIT DUAL LP 8MSOP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數:12 采樣率(每秒):3M 數據接口:- 轉換器數目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商設備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數目和類型:- |

| AD7921ARMZ-REEL7 | 功能描述:IC ADC 12BIT DUAL LP 8MSOP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:microPOWER™ 位數:8 采樣率(每秒):1M 數據接口:串行,SPI? 轉換器數目:1 功率耗散(最大):- 電壓電源:模擬和數字 工作溫度:-40°C ~ 125°C 安裝類型:表面貼裝 封裝/外殼:24-VFQFN 裸露焊盤 供應商設備封裝:24-VQFN 裸露焊盤(4x4) 包裝:Digi-Reel® 輸入數目和類型:8 個單端,單極 產品目錄頁面:892 (CN2011-ZH PDF) 其它名稱:296-25851-6 |

發布緊急采購,3分鐘左右您將得到回復。