- 您現在的位置:買賣IC網 > PDF目錄373960 > AD9224 (Analog Devices, Inc.) Complete 12-Bit 40 MSPS Monolithic A/D Converter PDF資料下載

參數資料

| 型號: | AD9224 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Complete 12-Bit 40 MSPS Monolithic A/D Converter |

| 中文描述: | 完整的12位40 MSPS的單片A / D轉換 |

| 文件頁數: | 19/24頁 |

| 文件大小: | 309K |

| 代理商: | AD9224 |

AD9224

–19–

REV. A

In this case an 80 MHz clock is divided by two to produce the

40 MHz clock input for the AD9224. In this configuration, the

duty cycle of the 80 MHz clock is irrelevant.

The input circuitry for the CLOCK pin is designed to accom-

modate CMOS inputs. The quality of the logic input, particu-

larly the rising edge, is critical in realizing the best possible jitter

performance of the part: the faster the rising edge, the better the

jitter performance.

As a result, careful selection of the logic family for the clock

driver, as well as the fanout and capacitive load on the clock

line, is important. Jitter-induced errors become more predomi-

nant at higher frequency, large amplitude inputs, where the

input slew rate is greatest.

Most of the power dissipated by the AD9224 is from the analog

power supplies. However, lower clock speeds will reduce digital

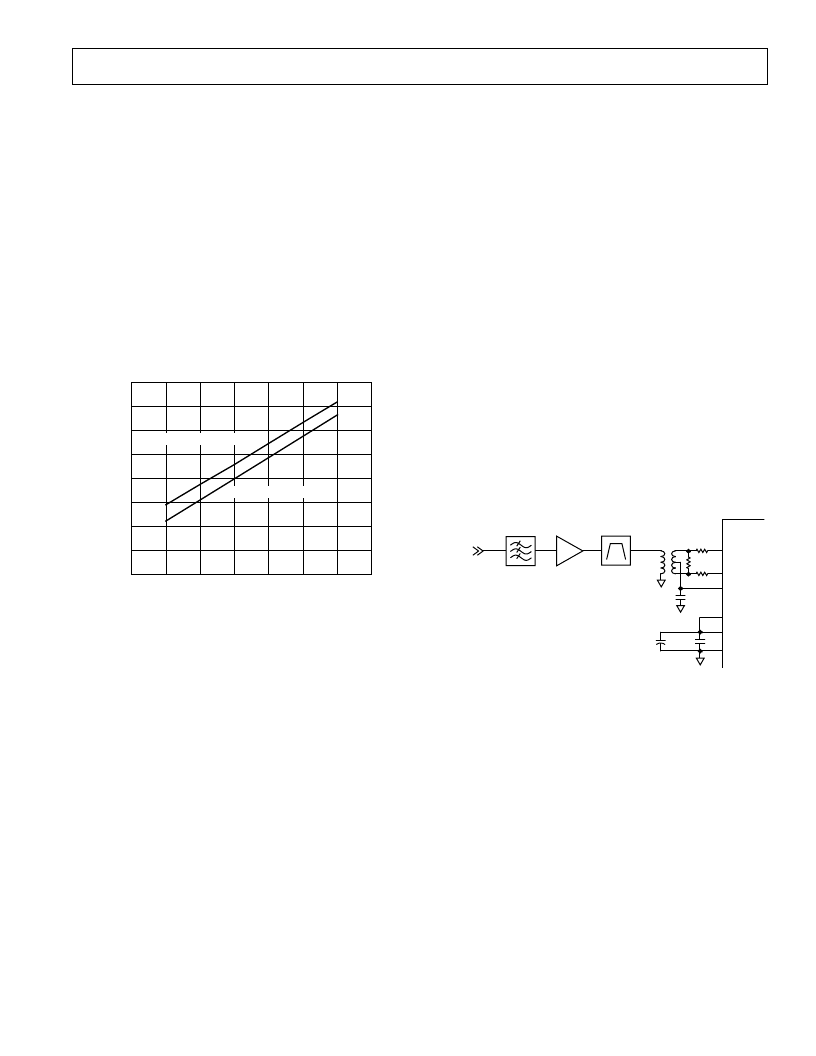

current. Figure 34 shows the relationship between power and

clock rate.

SAMPLE RATE – MHz

15

50

20

25

30

35

40

45

460

300

P

440

380

360

340

320

420

400

2V INTERNAL REFERENCE

1V INTERNAL REFERENCE

Figure 34. Power Consumption vs. Clock Rate

Direct IF Down Conversion Using the AD9224

Sampling IF signals above an ADC’s baseband region (i.e., dc

to F

S

/2) is becoming increasingly popular in communication

applications. This process is often referred to as Direct IF Down

Conversion or Undersampling. There are several potential ben-

efits in using the ADC to alias (or mix) down a narrowband or

wideband IF signal. First and foremost is the elimination of a

complete mixer stage with its associated baseband amplifiers

and filters, reducing cost and power dissipation. Second is the

ability to apply various DSP techniques to perform such func-

tions as filtering, channel selection, quadrature demodulation,

data reduction, detection, etc. A detailed discussion on using

this technique in digital receivers can be found in Analog De-

vices Application Notes AN-301 and AN-302.

In Direct IF Down Conversion applications, one exploits the

inherent sampling process of an ADC in which an IF signal

lying outside the baseband region can be aliased back into the

baseband region in a similar manner that a mixer will down-

convert an IF signal. Similar to the mixer topology, an image

rejection filter is required to limit other potential interfering

signals from also aliasing back into the ADC’s baseband region.

A tradeoff exists between the complexity of this image rejection

filter and the ADC’s sample rate as well as dynamic range.

The AD9224 is well suited for various IF sampling applications.

The AD9224’s low distortion input SHA has a full-power

bandwidth extending beyond 120 MHz, thus encompassing

many popular IF frequencies. A DNL of

±

0.7 LSB (typ) com-

bined with low thermal input referred noise allows the AD9224

in the 2 V span to provide 69 dB of SNR for a baseband input

sine wave. Also, its low aperture jitter of 4 ps rms ensures

minimum SNR degradation at higher IF frequencies. In fact,

the AD9224 is capable of still maintaining 64.5 dB of SNR at

an IF of 71 MHz with a 2 V input span. Note, although the

AD9224 can yield a 1 dB to 2 dB improvement in SNR when

configured for the larger 4 V span, the 2 V span achieves the

optimum full- scale distortion performance at these higher input

frequencies. Also, the 2 V span reduces the performance re-

quirements of the input driver circuitry (i.e., IP3) and thus may

also be more attractive from a system implementation perspective.

Figure 35 shows a simplified schematic of the AD9224 config-

ured in an IF sampling application. To reduce the complexity of

the digital demodulator in many quadrature demodulation ap-

plications, the IF frequency and/or sample rate are strategically

selected such that the bandlimited IF signal aliases back into the

center of the ADC’s baseband region (i.e., F

S

/4). For example,

if an IF signal centered at 45 MHz is sampled at 36 MSPS, an

image of this IF signal will be aliased back to 9.0 MHz, which

corresponds to one quarter of the sample rate (i.e., F

S

/4). This

demodulation technique typically reduces the complexity of the

post digital demodulator ASIC which follows the ADC.

OFILTER

SAW

LIHIGH

RF AMPLIFIER

PSTAGES

MIXER

200

V

20

V

20

V

0.1

m

F

MINIT4-6T

RF2317

VINA

VINB

CML

AD9224

0.1

m

F

10

m

F

VREF

SENSE

REFCOM

Figure 35. Example of AD9224 IF Sampling Circuit

To maximize its distortion performance, the AD9224 is config-

ured in the differential mode with a 2 V span using a transformer.

The center-tap of the transformer is biased at midsupply via the

CML output of the AD9224. Preceding the AD9224 and trans-

former is an optional bandpass filter as well as a gain stage. A

low Q passive bandpass filter can be inserted to reduce out-

of-band distortion and noise which lies within the AD9224’s

130 MHz bandwidth. A large gain stage(s) is often required to

compensate for the high insertion losses of a SAW filter used for

channel selection and image rejection. The gain stage will also

provide adequate isolation for the SAW filter from the charge

“kick back” currents associated with the AD9224’s switched

capacitor input stage.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9224-EB | Complete 12-Bit 40 MSPS Monolithic A/D Converter |

| AD9225 | Complete 12-Bit, 25 MSPS Monolithic A/D Converter |

| AD9225-EB | Complete 12-Bit, 25 MSPS Monolithic A/D Converter |

| AD9225AR | Complete 12-Bit, 25 MSPS Monolithic A/D Converter |

| AD9225ARS | Complete 12-Bit, 25 MSPS Monolithic A/D Converter |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9224ARS | 制造商:Analog Devices 功能描述:Analog/Digital Converter IC Number of Bi |

| AD9224ARSZ | 功能描述:IC ADC 12BIT 40MSPS 28-SSOP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:microPOWER™ 位數:8 采樣率(每秒):1M 數據接口:串行,SPI? 轉換器數目:1 功率耗散(最大):- 電壓電源:模擬和數字 工作溫度:-40°C ~ 125°C 安裝類型:表面貼裝 封裝/外殼:24-VFQFN 裸露焊盤 供應商設備封裝:24-VQFN 裸露焊盤(4x4) 包裝:Digi-Reel® 輸入數目和類型:8 個單端,單極 產品目錄頁面:892 (CN2011-ZH PDF) 其它名稱:296-25851-6 |

| AD9224ARSZRL | 功能描述:IC ADC 12BIT 40MSPS 28SSOP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:12 采樣率(每秒):300k 數據接口:并聯 轉換器數目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數目和類型:1 個單端,單極;1 個單端,雙極 |

| AD9224-EB | 制造商:Analog Devices 功能描述:Evaluation Kit For Complete 12-Bit, 40 MSPS Monolithic A/D Converter 制造商:Analog Devices 功能描述:EVAL KIT FOR COMPLETE 12-BIT, 40 MSPS MONOLITHIC A/D CNVRTR - Bulk 制造商:Rochester Electronics LLC 功能描述:12-BIT 40 MSPS MONOLITHIC A/D CONVERTER - Bulk |

| AD9224JR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog-to-Digital Converter, 12-Bit |

發布緊急采購,3分鐘左右您將得到回復。