- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373968 > AD9822JRS (ANALOG DEVICES INC) Complete 14-Bit CCD/CIS Signal Processor PDF資料下載

參數(shù)資料

| 型號(hào): | AD9822JRS |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | Complete 14-Bit CCD/CIS Signal Processor |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 封裝: | 5.30 MM, SSOP-28 |

| 文件頁(yè)數(shù): | 12/15頁(yè) |

| 文件大小: | 150K |

| 代理商: | AD9822JRS |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)

REV. A

AD9822

–12–

CIRCUIT OPERATION

Analog Inputs—CDS Mode

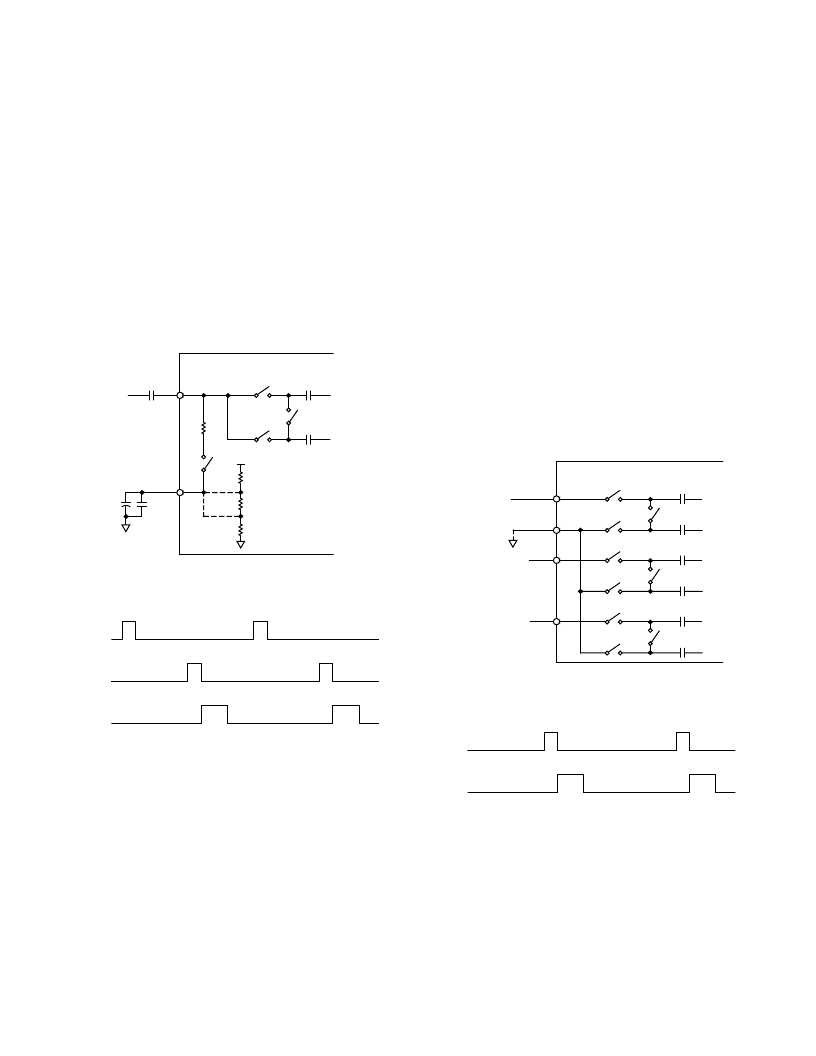

Figure 8 shows the analog input configuration for the CDS

mode of operation. Figure 9 shows the internal timing for the

sampling switches. The CCD reference level is sampled when

CDSCLK1 transitions from high to low, opening S1. The CCD

data level is sampled when CDSCLK2 transitions from high to

low, opening S2. S3 is then closed, generating a differential output

voltage representing the difference between the two sampled levels.

The input clamp is controlled by CDSCLK1. When CDSCLK1

is high, S4 closes and the internal bias voltage is connected to

the analog input. The bias voltage charges the external 0.1

μ

F

input capacitor, level-shifting the CCD signal into the AD9822’s

input common-mode range. The time constant of the input

clamp is determined by the internal 5 k

resistance and the

external 0.1

μ

F input capacitance.

AD9822

S1

S2

2pF

S3

2pF

CML

CML

AVDD

4V

S4

5k

V

1.7k

V

VINR

OFFSET

C

IN

0.1

m

F

CCD SIGNAL

0.1

m

F

1

m

F

+

3V

2.2k

V

6.9k

V

INPUT CLAMP LEVEL

IS SELECTED IN THE

CONFIGURATION

REGISTER

Figure 8. CDS-Mode Input Configuration (All Three Chan-

nels Are Identical)

CDSCLK1

CDSCLK2

Q3

(INTERNAL)

S1, S4 CLOSED

S1, S4 CLOSED

S2 CLOSED

S2 CLOSED

S3 CLOSED

S3 CLOSED

S3 OPEN

S2 OPEN

S1, S4 OPEN

Figure 9. CDS-Mode Internal Switch Timing

External Input Coupling Capacitors

The recommended value for the input coupling capacitors is

0.1

μ

F. While it is possible to use a smaller capacitor, this larger

value is chosen for several reasons:

1.

Signal Attenuation

. The input coupling capacitor creates a

capacitive divider with a CMOS integrated circuit’s input

capacitance, attenuating the CCD signal level. C

IN

should be

large relative to the IC’s 10 pF input capacitance in order to

minimize this effect.

2.

Linearity

. Some of the input capacitance of a CMOS IC is

junction capacitance, which varies nonlinearly with applied

voltage. If the input coupling capacitor is too small, then the

attenuation of the CCD signal will vary nonlinearly with signal

level. This will degrade the system linearity performance.

3.

Sampling Errors

. The internal 2 pF sample capacitors have

a “memory” of the previously sampled pixel. There is a

charge redistribution error between C

IN

and the internal

sample capacitors

for larger pixel-to-pixel voltage swings. As

the value of C

IN

is reduced, the resulting error in the sampled

voltage will increase. With a C

IN

value of 0.1

μ

F, the charge

redistribution error will be less than 1 LSB for a full-scale

pixel-to-pixel voltage swing.

Analog Inputs—SHA Mode

Figure 10 shows the analog input configuration for the SHA

mode of operation. Figure 11 shows the internal timing for the

sampling switches. The input signal is sampled when CDSCLK2

transitions from high to low, opening S1. The voltage on the

OFFSET pin is also sampled on the falling edge of CDSCLK2,

when S2 opens. S3 is then closed, generating a differential out-

put voltage representing the difference between the sampled

input voltage and the OFFSET voltage. The input clamp is

disabled during SHA mode operation.

AD9822

S1

2pF

S3

CML

VINR

INPUT SIGNAL

S2

2pF

CML

OFFSET

RED

VING

GREEN

VINB

BLUE

OPTIONAL DC OFFSET

(OR CONNECT TO GND)

Figure 10. SHA-Mode Input Configuration (All Three

Channels Are Identical)

CDSCLK2

Q3

(INTERNAL)

S1, S2 CLOSED

S1, S2 CLOSED

S3 CLOSED

S3 CLOSED

S3 OPEN

S1, S2 OPEN

Figure 11. SHA-Mode Internal Switch Timing

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9823 | Correlated Double Sampler (CDS) |

| AD9823BRUZ | Correlated Double Sampler (CDS) |

| AD9824KCP | Complete 14-Bit 30 MSPS CCD Signal Processor |

| AD9824 | Complete 14-Bit 30 MSPS CCD Signal Processor |

| AD9826KRS | Complete 16-Bit Imaging Signal Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9822JRSRL | 制造商:Analog Devices 功能描述:AFE Video 1ADC 14-Bit 5V 28-Pin SSOP T/R 制造商:Rochester Electronics LLC 功能描述:14 BIT AFE WITH 12 BIT LINEARITY - Bulk |

| AD9822JRSZ | 功能描述:IC CCD SIGNAL PROC 14BIT 28SSOP RoHS:是 類別:集成電路 (IC) >> 接口 - 傳感器和探測(cè)器接口 系列:- 其它有關(guān)文件:Automotive Product Guide 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:74 系列:- 類型:觸控式傳感器 輸入類型:數(shù)字 輸出類型:數(shù)字 接口:JTAG,串行 電流 - 電源:100µA 安裝類型:表面貼裝 封裝/外殼:20-TSSOP(0.173",4.40mm 寬) 供應(yīng)商設(shè)備封裝:20-TSSOP 包裝:管件 |

| AD9822JRSZRL | 功能描述:IC CCD SIGNAL PROC 14BIT 28SSOP RoHS:是 類別:集成電路 (IC) >> 接口 - 傳感器和探測(cè)器接口 系列:- 其它有關(guān)文件:Automotive Product Guide 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:74 系列:- 類型:觸控式傳感器 輸入類型:數(shù)字 輸出類型:數(shù)字 接口:JTAG,串行 電流 - 電源:100µA 安裝類型:表面貼裝 封裝/外殼:20-TSSOP(0.173",4.40mm 寬) 供應(yīng)商設(shè)備封裝:20-TSSOP 包裝:管件 |

| AD9822JRZ | 制造商:Analog Devices 功能描述:AFE Video 1ADC 14-Bit 5V 28-Pin SOIC W |

| AD9822JRZRL | 制造商:Analog Devices 功能描述:AFE Video 1ADC 14-Bit 5V 28-Pin SOIC W T/R |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。