- 您現在的位置:買賣IC網 > PDF目錄373969 > AD9859YSV (ANALOG DEVICES INC) 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer PDF資料下載

參數資料

| 型號: | AD9859YSV |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理外設 |

| 英文描述: | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| 中文描述: | DSP-NUM CONTROLLED OSCILLATOR, PQFP48 |

| 封裝: | EXPOSED PAD, PLASTIC, MS-026ABC, QFP-48 |

| 文件頁數: | 4/24頁 |

| 文件大小: | 574K |

| 代理商: | AD9859YSV |

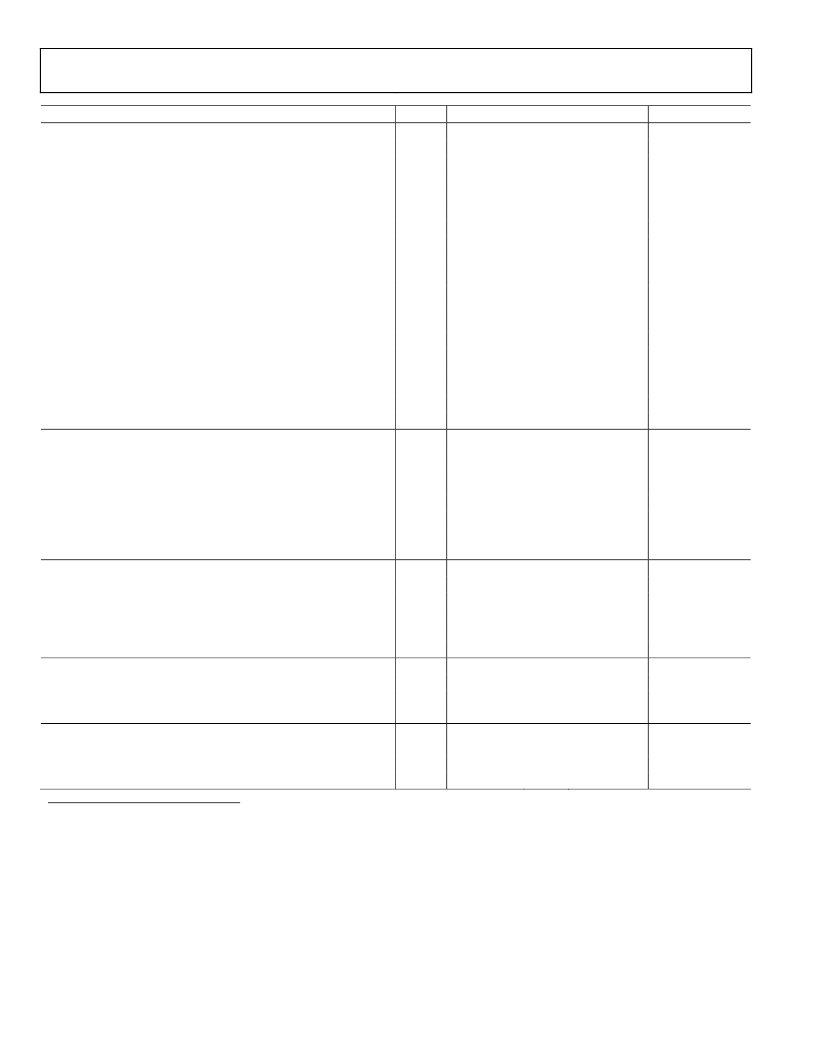

AD9859

Parameter

TIMING CHARACTERISTICS

Serial Control Bus

Maximum Frequency

Minimum Clock Pulse Width Low

Minimum Clock Pulse Width High

Maximum Clock Rise/Fall Time

Minimum Data Setup Time DVDD_I/O = 3.3 V

Minimum Data Setup Time DVDD_I/O = 1.8 V

Minimum Data Hold Time

Maximum Data Valid Time

Wake-Up Time

2

Minimum Reset Pulse Width High

I/O UPDATE to SYNC_CLK Setup Time DVDD_I/O = 3.3 V

I/O UPDATE to SYNC_CLK Setup Time DVDD_I/O = 3.3 V

I/O UPDATE, SYNC_CLK Hold Time

Latency

I/O UPDATE to Frequency Change Prop Delay

I/O UPDATE to Phase Offset Change Prop Delay

I/O UPDATE to Amplitude Change Prop Delay

CMOS LOGIC INPUTS

Logic 1 Voltage @ DVDD_I/O (Pin 43) = 1.8 V

Logic 0 Voltage @ DVDD_I/O (Pin 43) = 1.8 V

Logic 1 Voltage @ DVDD_I/O (Pin 43) = 3.3 V

Logic 0 Voltage @ DVDD_I/O (Pin 43) = 3.3 V

Logic 1 Current

Logic 0 Current

Input Capacitance

CMOS LOGIC OUTPUTS (1 mA Load) DVDD_I/O = 1.8 V

Logic 1 Voltage

Logic 0 Voltage

CMOS LOGIC OUTPUTS (1 mA Load) DVDD_I/O = 3.3 V

Logic 1 Voltage

Logic 0 Voltage

POWER CONSUMPTION (AVDD = DVDD = 1.8 V)

Single-Tone Mode

Rapid Power-Down Mode

Full-Sleep Mode

SYNCHRONIZATION FUNCTION

4

Maximum SYNC Clock Rate (DVDD_I/O = 1.8 V)

Maximum SYNC Clock Rate (DVDD_I/O = 3.3 V)

SYNC_CLK Alignment Resolution

5

Rev. 0 | Page 4 of 24

Temp

FULL

FULL

FULL

FULL

FULL

FULL

FULL

FULL

FULL

FULL

FULL

FULL

FULL

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

25°C

Min

7

7

3

5

0

5

4

6

0

24

24

16

1.25

2.2

1.35

2.8

62.5

100

Typ

25

2

25

1

3

2

162

150

20

±1

Max

0.6

0.8

12

12

0.4

0.4

171

160

27

Unit

Mbps

ns

ns

ns

ns

ns

ns

ns

ms

SYSCLK Cycles

3

ns

ns

ns

SYSCLK Cycles

SYSCLK Cycles

SYSCLK Cycles

V

V

V

V

μA

μA

pF

V

V

V

V

mW

mW

mW

MHz

MHz

SYSCLK Cycles

1

To achieve the best possible phase noise, the largest amplitude clock possible should be used. Reducing the clock input amplitude reduces the phase noise perform-

ance of the device.

2

Wake-up time refers to the recovery from analog power-down modes (see the Power-Down Functions of the AD9859 section). The longest time required is for the

reference clock multiplier PLL to relock to the reference. The wake-up time assumes that there is no capacitor on DACBP and that the recommended PLL loop filter

values are used.

3

SYSCLK cycle refers to the actual clock frequency used on-chip by the DDS. If the reference clock multiplier is used to multiply the external reference clock frequency,

the SYSCLK frequency is the external frequency multiplied by the reference clock multiplication factor. If the reference clock multiplier is not used, the SYSCLK fre-

quency is the same as the external reference clock frequency.

4

SYNC_CLK = SYSCLK rate. For SYNC_CLK rates ≥ 50 MHz, the high speed sync enable bit, CFR2<11>, should be set.

5

This parameter indicates that the digital synchronization feature cannot overcome phase delays (timing skew) between system clock rising edges. If the system clock

edges are aligned, the synchronization function should not increase the skew between the two edges.

相關PDF資料 |

PDF描述 |

|---|---|

| AD9859YSV-REEL7 | 400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9862PCB | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9860 | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9860BST | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

| AD9860PCB | Mixed-Signal Front-End (MxFE⑩) Processor for Broadband Communications |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9859YSV-REEL7 | 制造商:AD 制造商全稱:Analog Devices 功能描述:400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

| AD9859YSVZ | 功能描述:IC DDS DAC 10BIT 400MSPS 48-TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

| AD9859YSVZ | 制造商:Analog Devices 功能描述:IC 400 MSPS DDS 制造商:Analog Devices 功能描述:IC, 400 MSPS DDS |

| AD9859YSVZ | 制造商:Analog Devices 功能描述:DIRECT DIGITAL SYNTHESIZER |

| AD9859YSVZ1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:400 MSPS, 10-Bit,1.8 V CMOS Direct Digital Synthesizer |

發布緊急采購,3分鐘左右您將得到回復。