- 您現在的位置:買賣IC網 > PDF目錄373972 > AD9957 (Analog Devices, Inc.) 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC PDF資料下載

參數資料

| 型號: | AD9957 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| 中文描述: | 1 GSPS的正交數字上變頻器與18位智商數據路徑和14位DAC |

| 文件頁數: | 21/60頁 |

| 文件大小: | 840K |

| 代理商: | AD9957 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

AD9957

Rev. 0 | Page 21 of 60

t

DH

I

0

TxENABLE

PDCLK

D<13:0>

I

K

I

K – 1

I

3

I

2

I

1

0

t

DH

t

DS

t

DS

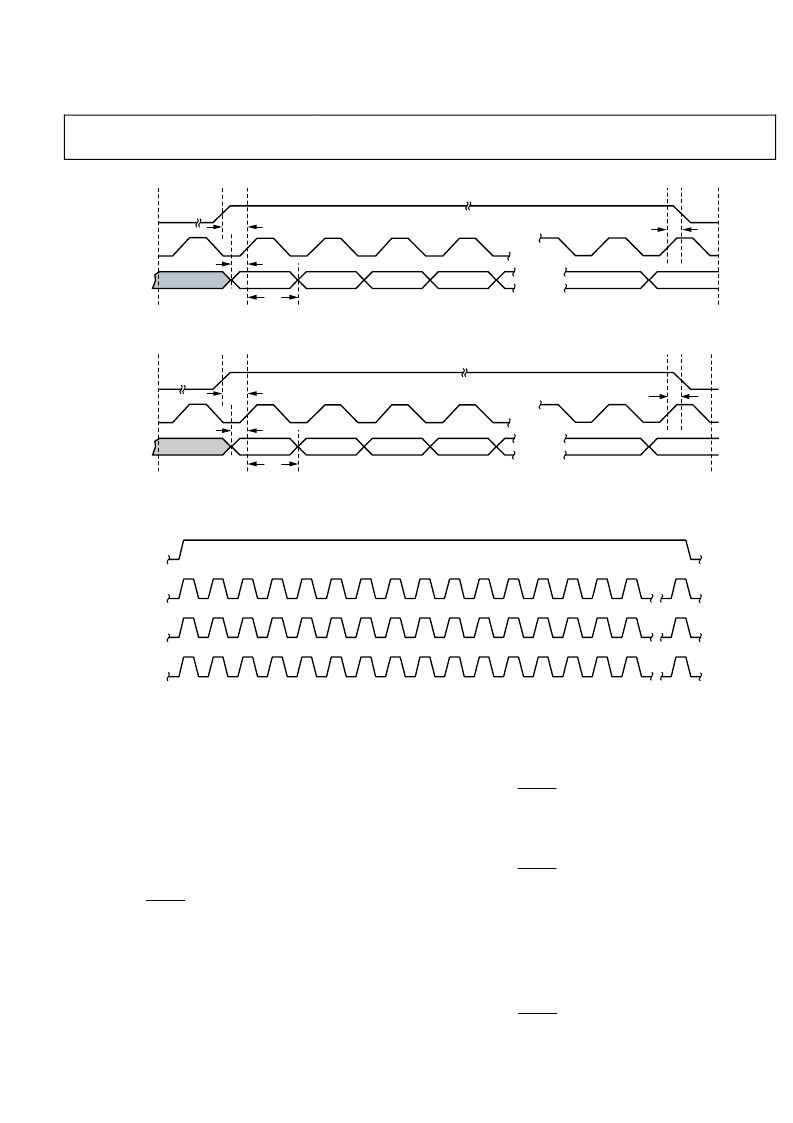

Figure 30. 18-Bit Parallel Port Timing Diagram—Interpolating DAC Mode

t

DH

I

0

TxENABLE

PDCLK

D<13:0>

Q

N

I

N

Q

1

I

1

Q

0

0

t

DH

t

DS

t

DS

Figure 31. 18-Bit Parallel Port Timing Diagram—Quadrature Modulation Mode

TxENABLE

PDCLK

I DATA

Q DATA

Q

0

Q

1

Q

2

Q

3

Q

4

Q

6

Q

5

Q

7

Q

8

Q

9

Q

10

Q

11

Q

12

Q

13

Q

14

Q

15

I

0

I

1

I

2

I

3

I

4

I

6

I

5

I

7

I

8

I

9

I

10

I

11

I

12

I

13

I

14

I

15

I

16n – 1

Q

16n – 1

0

Figure 32. Dual Serial I/Q Bit Stream Timing Diagram, BFI Mode

INPUT DATA ASSEMBLER

The input to the AD9957 is an 18-bit parallel data port in

QDUC or interpolating DAC modes. In BFI mode, it operates

as a dual serial data port.

In QDUC mode, it is assumed that two consecutive 18-bit

words represent the real (I) and imaginary (Q) parts of a

complex number of the form, I + jQ. The 18-bit words are

supplied to the input of the AD9957 at a rate of

f

f

PDCLK

2

R

SYSCLK

=

for QDUC mode

where:

f

SYSCLK

(for all of the PDCLK equations in this section) is the

sample rate of the DAC.

R

(for all of the PDCLK equations in this section) is the

interpolation factor of the programmable interpolation filter.

When the PDCLK rate control bit is active in QDUC mode,

however, the frequency of PDCLK becomes

f

f

PDCLK

4

R

SYSCLK

=

with PDCLK rate control active

In the interpolating DAC mode, the rate of PDCLK is the same

as QDUC mode with the PDCLK rate control bit active, that is

f

f

PDCLK

4

R

SYSCLK

=

for interpolating DAC mode

In BFI mode, the 18-bit parallel input converts to a dual serial

input. That is, one pin is assigned as the serial input for the I-words

and one pin is assigned as the serial input for the Q-words. The

other 16 pins are not used. Furthermore, each I- and Q-word

has a 16-bit resolution. f

PDCLK

is the bit rate of the I- and Q-data

streams and is given by

f

f

(for BFI mode)

R

SYSCLK

PDCLK

=

相關PDF資料 |

PDF描述 |

|---|---|

| AD9957BSVZ | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| AD9957BSVZ-REEL | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| AD9957_07 | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| AD9958BCPZ-REEL7 | 2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9958 | 2-Channel 500 MSPS DDS with 10-Bit DACs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9957/PCBZ | 功能描述:BOARD EVAL AD9957 QUADRATURE MOD RoHS:是 類別:編程器,開發系統 >> 評估演示板和套件 系列:AgileRF™ 標準包裝:1 系列:PSoC® 主要目的:電源管理,熱管理 嵌入式:- 已用 IC / 零件:- 主要屬性:- 次要屬性:- 已供物品:板,CD,電源 |

| AD9957_07 | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| AD9957BCPZ | 制造商:Analog Devices 功能描述:GSPS QUADRATURE DIGITAL UPCONVERTER W/18-BIT IQ DATA PATH - Trays |

| AD9957BSVZ | 功能描述:IC DDS 1GSPS 14BIT IQ 100TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

| AD9957BSVZ-REEL | 功能描述:IC DDS 1GSPS 14BIT IQ 100TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

發布緊急采購,3分鐘左右您將得到回復。