- 您現在的位置:買賣IC網 > PDF目錄373972 > AD9957 (Analog Devices, Inc.) 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC PDF資料下載

參數資料

| 型號: | AD9957 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| 中文描述: | 1 GSPS的正交數字上變頻器與18位智商數據路徑和14位DAC |

| 文件頁數: | 41/60頁 |

| 文件大小: | 840K |

| 代理商: | AD9957 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

AD9957

which three AD9957s are synchronized with one device operating

as a master timing unit and the others as slave units.

Rev. 0 | Page 41 of 60

The master device must have its SYNC_IN pins included as part

of the synchronization distribution and delay equalization mecha-

nism for it to be synchronized with the slave units.

The synchronization mechanism begins with the clock distribu-

tion and delay equalization block, which ensures that all devices

receive an edge aligned REFCLK signal. However, even though

the REFCLK signal is edge aligned among all devices, this alone

does not guarantee that the clock state of each internal clock

generator is coordinated with the others. This is the role of the

synchronization and delay equalization block. This block accepts

the SYNC_OUT signal generated by the master device and

redistributes it to the SYNC_IN input of the slave units (as well

as feeding it back to the master). The goal of the redistributed

SYNC_OUT signal from the master device is to deliver an edge

aligned SYNC_IN signal to all of the sync receivers.

Assuming that all devices share the same REFCLK edge (due to

the clock distribution and delay equalization block) and that all

devices share the same SYNC_IN edge (due to the synchroniza-

tion and delay equalization block), then all devices should be

generating an internal sync pulse in unison (assuming they all

have the same sync receiver delay value). With the further

stipulation that all devices have the same sync state preset value,

then the synchronized sync pulses cause all of the devices to

assume the same predefined clock state simultaneously. That is,

the internal clocks of all devices are fully synchronized.

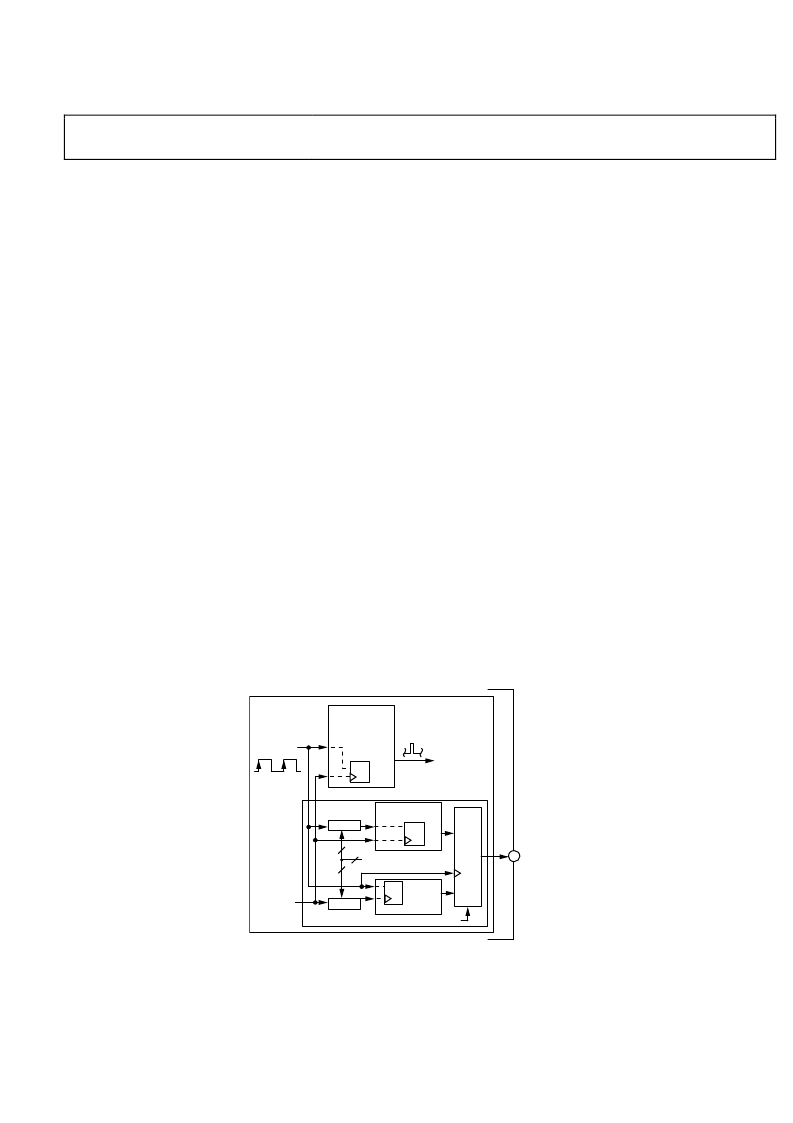

The synchronization mechanism depends on the reliable

generation of a sync pulse by the edge detection block in the

sync receiver. Generation of a valid sync pulse, however,

requires proper sampling of the rising edge of the delayed

sync-in signal with the rising edge of the local SYSCLK. If the

edge timing of these signals fails to meet the setup or hold time

requirements of the internal latches in the edge detection

circuitry, then the proper generation of the sync pulse is in

jeopardy. The setup-and-hold validation block (see Figure 58)

gives the user a means to validate that proper edge timing exists

between the two signals. The setup-and-hold validation block

can be disabled via the sync timing validation disable bit in Control

Function Register 2.

The validation block makes use of a user-specified time window

(programmable in increments of ~150 ps via the 4-bit sync

validation delay word in the multichip sync register). The setup

validation and hold validation circuits use latches identical to

those in the rising edge detector and strobe generator. The

programmable time window is used to skew the timing between

the rising edges of the local SYSCLK signal and the rising edges

of the delayed sync-in signal. If either the hold or setup valida-

tion circuits fail to detect a valid edge sample, the condition is

indicated externally via the SYNC_SMP_ERR pin (active high).

The user must choose a sync validation delay value that is a

reasonable fraction of the SYSCLK period. For example, if the

SYSCLK frequency is 1 GHz (1 ns period), then a reasonable

value is 1 or 2 (150 ps or 300 ps). Choosing too large a value can

cause the SYNC_SMP_ERR pin to generate false error signals.

Choosing too small a value may cause instability.

SYNC

PULSE

SYSCLK

DELAY

DELAY

C

4

SYNC VALIDATION

DELAY

4

4

SYNC_SMP_ERR

SYNC RECEIVER

12

SYNC TIMING VALIDATION DISABLE

SETUP

VALIDATION

HOLD

VALIDATION

D Q

SETUP AND HOLD VALIDATION

TO

CLOCK

GENERATION

LOGIC

FROM

SYNC

RECEIVER

DELAY

LOGIC

D Q

D Q

RISING EDGE

DETECTOR

AND STROBE

GENERATOR

0

Figure 58. Sync Timing Validation Block

相關PDF資料 |

PDF描述 |

|---|---|

| AD9957BSVZ | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| AD9957BSVZ-REEL | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| AD9957_07 | 1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| AD9958BCPZ-REEL7 | 2-Channel 500 MSPS DDS with 10-Bit DACs |

| AD9958 | 2-Channel 500 MSPS DDS with 10-Bit DACs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9957/PCBZ | 功能描述:BOARD EVAL AD9957 QUADRATURE MOD RoHS:是 類別:編程器,開發系統 >> 評估演示板和套件 系列:AgileRF™ 標準包裝:1 系列:PSoC® 主要目的:電源管理,熱管理 嵌入式:- 已用 IC / 零件:- 主要屬性:- 次要屬性:- 已供物品:板,CD,電源 |

| AD9957_07 | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Quadrature Digital Upconverter with 18-Bit IQ Data Path and 14-Bit DAC |

| AD9957BCPZ | 制造商:Analog Devices 功能描述:GSPS QUADRATURE DIGITAL UPCONVERTER W/18-BIT IQ DATA PATH - Trays |

| AD9957BSVZ | 功能描述:IC DDS 1GSPS 14BIT IQ 100TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

| AD9957BSVZ-REEL | 功能描述:IC DDS 1GSPS 14BIT IQ 100TQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 直接數字合成 (DDS) 系列:- 產品變化通告:Product Discontinuance 27/Oct/2011 標準包裝:2,500 系列:- 分辨率(位):10 b 主 fclk:25MHz 調節字寬(位):32 b 電源電壓:2.97 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-TSSOP(0.173",4.40mm 寬) 供應商設備封裝:16-TSSOP 包裝:帶卷 (TR) |

發布緊急采購,3分鐘左右您將得到回復。